### **CPS&IoT'2019**

Summer School on Cyber-Physical Systems and Internet-of-Things Budva, Montenegro, June 10-14, 2019

## Proceedings of the Summer School on Cyber-Physical Systems and Internet-of-Things

#### Vol. I

#### **Editors**

Lech Jóźwiak, Chairmen of the CPS&IoT'2019

Eindhoven University of Technology, The Netherlands

and

Radovan Stojanović University of Montenegro, Montenegro

#### CPS&IoT'2019

### Summer School on Cyber-Physical Systems and Internet-of-Things Budva, Montenegro, June 10-14, 2019

#### **Chairmen Introduction**

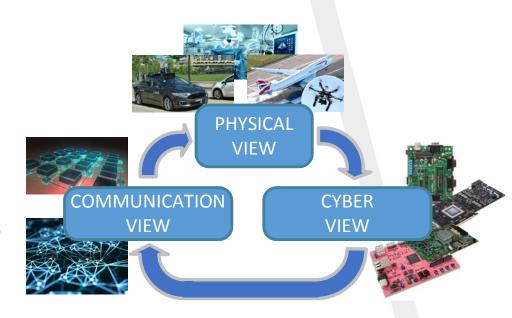

**Cyber** comes from Greek adjective kyberneticos (cybernetic) which means skilled in steering or governing. Already from ancient times people constructed various machines (physical systems) and their controllers (cyber systems). **Cyber-physical system (CPS)** is a compound system engineered through integration of cyber and physical sub-systems or components, so that it appears and operates as a single unit in relation to the external world (to other systems).

With the progress of time, machines and their controllers became more and more complex. Until the end of the 19th century the controllers (cyber systems) were implemented as mechanical, hydraulic and pneumatic systems. In the 20th century they started to be gradually replaced by the electric controllers, and later by the electronic controllers. Introduction of transistors and integrated circuit technologies in the years 1950s and 1960s, correspondingly, enabled the microelectronics and information technology revolution that is progressing according to the Moore's low till now. The revolutionary progress in computing platforms, communication, networking, sensors and actuators enabled much more effective and efficient CPS for traditional applications, and "smart", sophisticated and affordable CPS for numerous new applications, e.g. smart communicating robots, cars, wearable and implantable medical devices, etc.

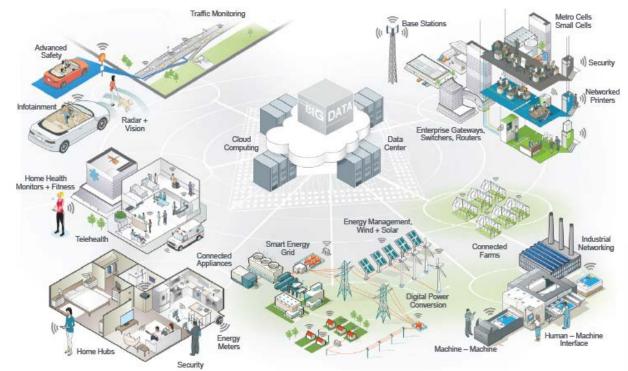

Contemporary cyber-physical systems (CPS) are smart compound systems engineered through seamless integration of embedded information processing sub-systems and physical sub-systems. The modern smart collaborating CPS, that started to form the Cyber-Physical Systems of Systems (CPSoS) and Internet of Things (IoT), have important applications in virtually all economic and social segments, and their huge economic and societal impact rapidly increases. The CPS and IoT area undergoes a revolutionary development. There is however a common opinion that many more well-trained researchers and developers are needed in this rapidly developing area, as well as, more information exchange and collaboration among different projects and teams in the area.

### This Summer School on Cyber-Physical Systems and Internet-of-Things (CPS&IoT'2019) aims at serving the following main purposes:

- advanced training of industrial and academic researchers, developers, engineers and decision-makers; academic teachers, Ph.D. and M.Sc. students; entrepreneurs, investors, research funding agents, and policy makers; and other participants who want to learn about CPS and IoT engineering;

- dissemination, exchange and discussion of advanced knowledge and project results from numerous European R&D projects in CPS and IoT;

- promotion and facilitation of international contacts and collaboration among people working or interested in the CPS and IoT area.

The school is open to everybody, but previous knowledge or equivalent practical experience at least at the Bachelor level in engineering (e.g. system, computer, electronic, electrical, automotive, aviation, mechanical, or industrial engineering), computer science, informatics, applied physics or similar is recommended.

**Industry Participation is encouraged.** CPS&IoT'2019 Summer School is not only to follow courses and learn new knowledge on CPS and IoT from top professionals, but to meet people, interact and discuss with outstanding researchers, developers, academic lecturers, advanced students, and other

participants, collaborate or start collaborations, and meet many talented people who may become employees of your companies as well.

**Distinguishing features of this advanced Summer School** are that its *lectures, demonstrations, and practical hands-on sessions* will be given by *top European specialists* in particular CPS and IoT fields *form industry and academia*, and will deliver *very fresh advanced knowledge*. They are based on *results from numerous currently running or recently finished European R&D projects in CPS and IoT*, what gives an excellent opportunity to get acquainted with issues and challenges of CPS and IoT development; actual industrial problems, designs and case studies; and new concepts, advanced knowledge and modern design methods and tools created in the European R&D projects.

**CPS&IoT'2019 Summer School is collocated with** ECYPS2019 – 7th EUROMICRO/IEEE Workshop on Embedded and Cyber-Physical Systems, and MECO2019 – 8th Mediterranean Conference on Embedded Computing. The Summer School participants are encouraged to submit their papers to ECYPS2019 and MECO2019: <a href="http://embeddedcomputing.me/en">http://embeddedcomputing.me/en</a>.

The CPS&IoT'2019 Summer School Program is composed of four days of lectures, demonstrations, practical hands-on sessions, and discussions, as well as free participation in ECYPS 2019 and MECO 2019 sessions. The topics of the lectures, demonstrations, and practical hands-on sessions cover major CPS applications (focusing on modern mobile applications that require high-performance or low energy consumption, as well as, high reliability, security and safety), computing technology for modern CPS, CPS architectures, development problems and solutions, as well as, design methodologies and design tools for all CPS design phases. Detailed list of the CPS&IoT'2019 Presentations including the names of their authors and presenters is provided in the Schedule of the CPS&IoT'2019 Summer School.

Venue of CPS&IoT'2019 is Hotel Budva\*\*\*\*\*, Budva, Montenegro. Budva is a 3500 years old town located at the Adriatic Sea coast of Montenegro. It is a popular touristic destination, with its charming Old Town, beautiful natural environment, 35 clean sandy beaches, and proximity to many famous touristic attractions as Kotor, Boka Kotorska, Sveti Stefan, Dubrovnik, and several national parks. It is an excellent place to have a summer school in a relaxed and friendly atmospheer. For accomodation Hotel Budva\*\*\*\* and Hotel Slovenska Plaza\*\*\*\* are advised, but there are many other accommodation possibilities in Budva. Budva is very well accessible by plane. Podgorica Airport is about 65 km from Budva and it receives regular flights from Vienna, Paris, Rome, Zürich, Frankfurt, Warsaw, Ljubljana, Belgrade, and Instabul, while Tivat Airport (about 20km from Budva) and Dubrovnik Airport (65km from Budva) are very frequent vacation and charter flight destinations during the summer time.

More information can be found at the CPS&IoT'2019 Summer School web-site: http://embeddedcomputing.me/en/cps-iot.

This Summer School is possible thanks to involvement of many outstanding researchers and developers from multiple European countries, R&D projects and teams. The Chairmen of the CPS&IoT'2019 Summer School express their thanks to all authors and presenters of the CPS&IoT'2019 presentations, as well as, to all other people who contributed to the success of the Summer School, and wish a very effective and pleasant Summer School time to all the CPS&IoT'2019 participants.

Lech Jóźwiak Eindhoven University of Technology, The Netherlands and Radovan Stojanović University of Montenegro, Montenegro

### Contents

Lech Jóźwiak, Introduction to Modern Cyber-Physical Systems and their Quality-Driven Design, 1

Henk Corporaal, Embedded Processors for Cyber-Physical Systems, 66

*Jiří KadlecKadlec*, *Zdeněk Pohl*, *Lukáš Lukáš Kohout*, Implementation of Implementation of HW - accelerated video -processing on industrial Zynq modules, 127

Francesca Palumbo, Claudio Rubattu, Carlo Sau, Tiziana Fanni, Luigi Raffo, Dataflow-Based Toolchain for Based Toolchain for Adaptive Accelerators, 149

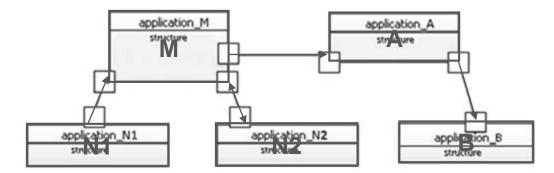

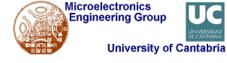

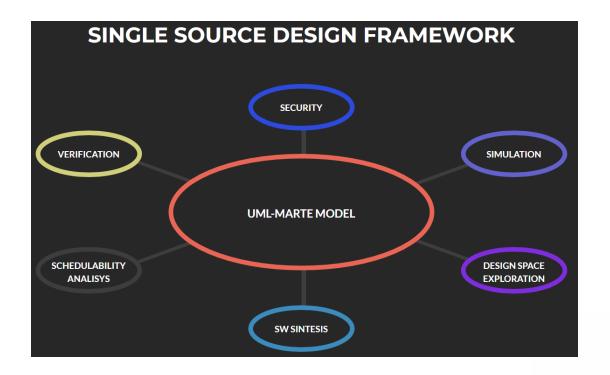

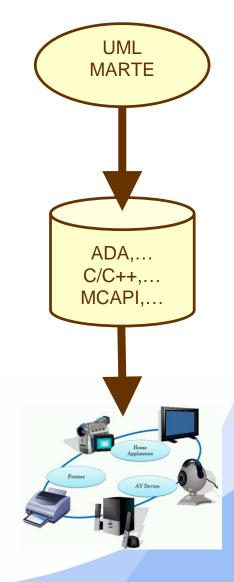

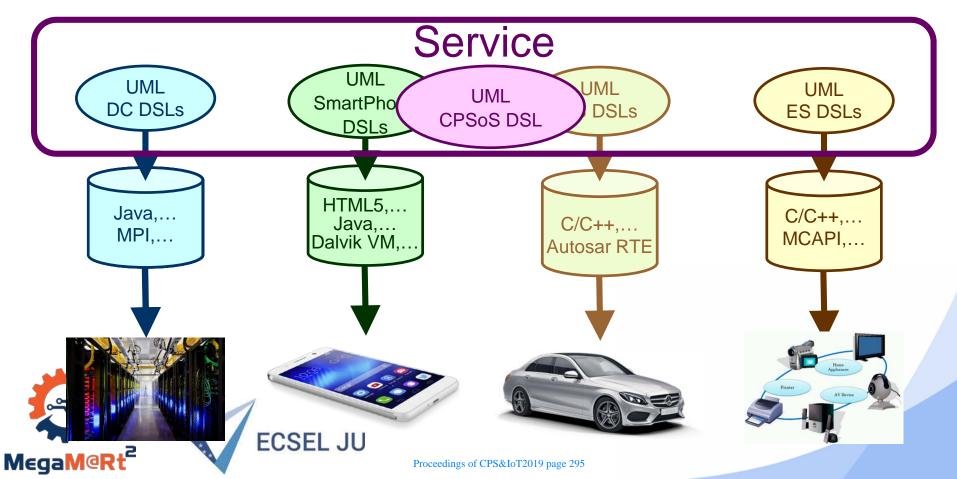

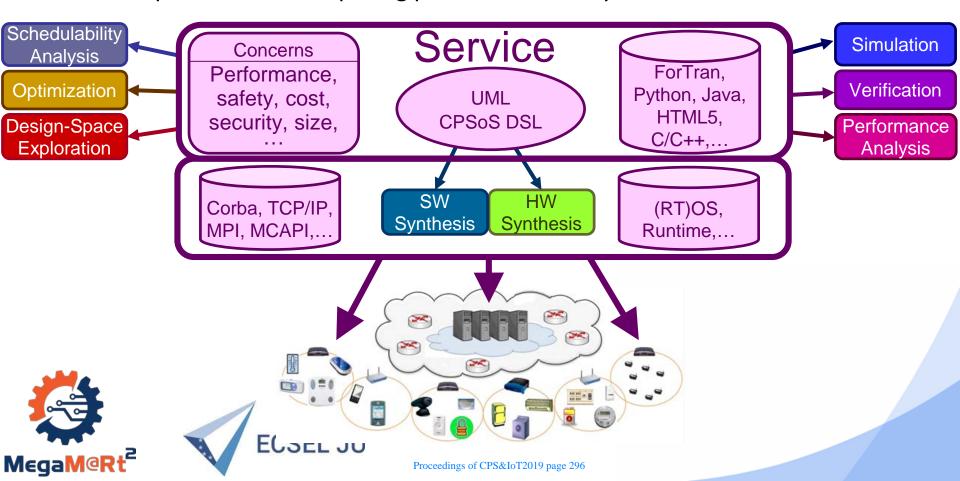

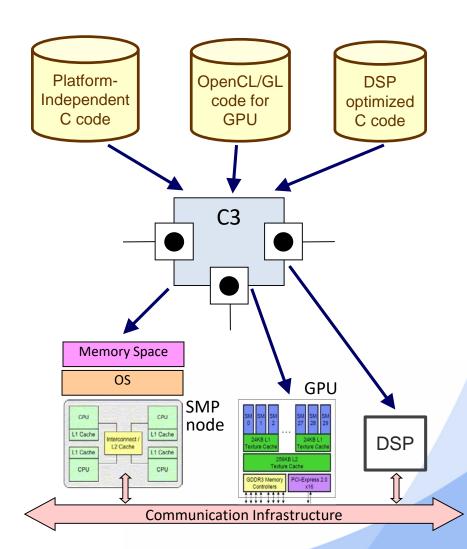

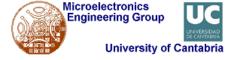

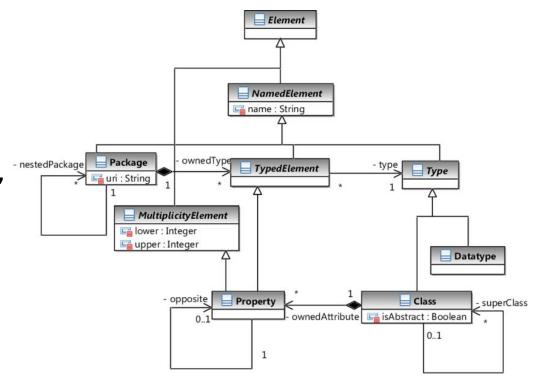

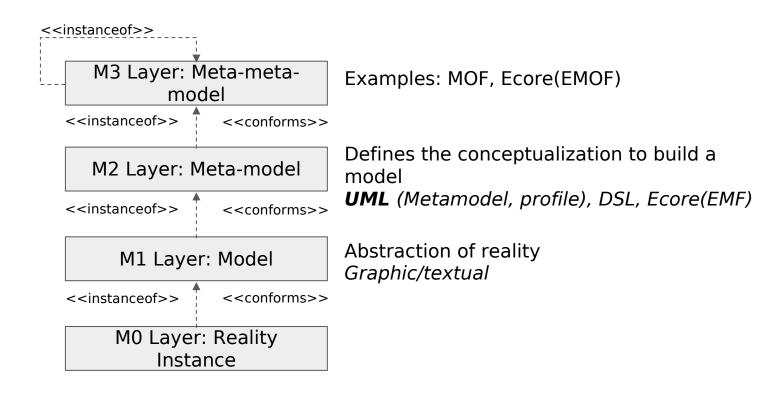

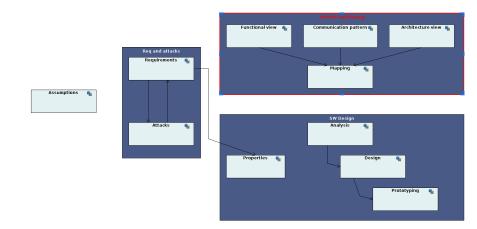

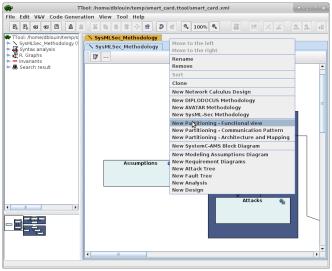

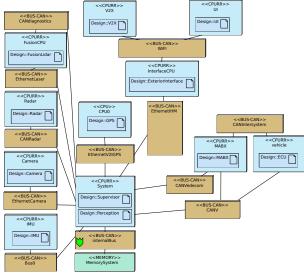

Eugenio Villar, Megamodelingof complex, distributed, heterogeneous CPS systems, 288

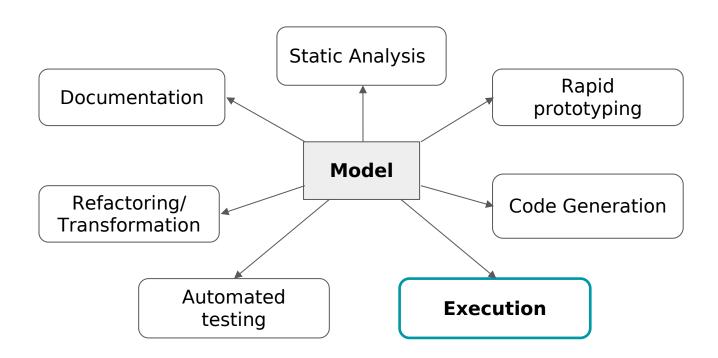

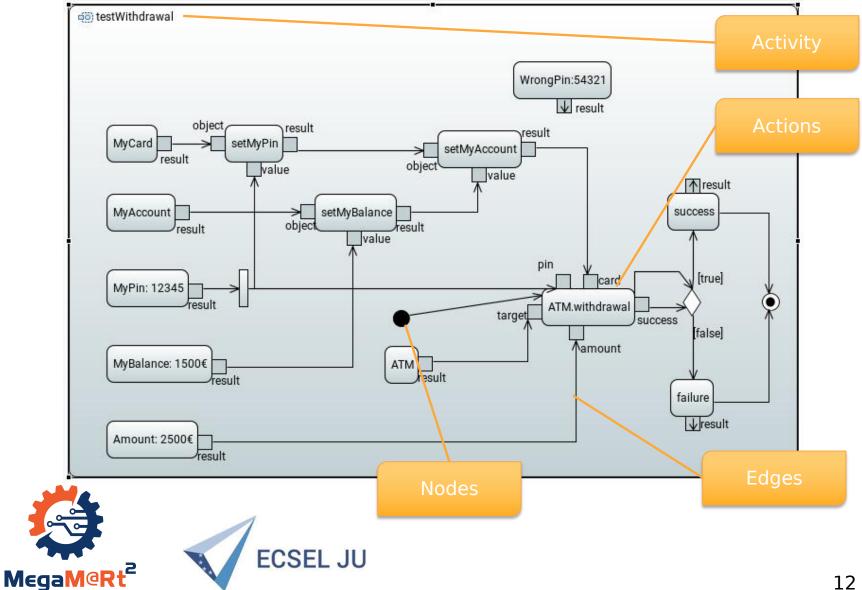

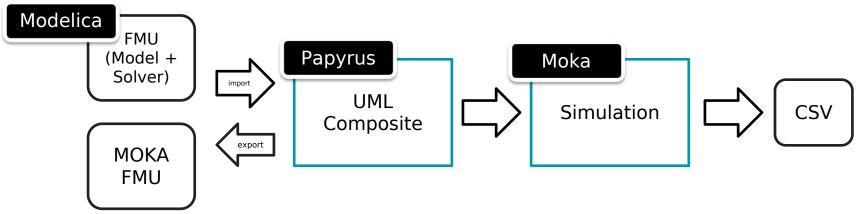

Jesús Gorroñogoitia, Execution of software models, 308

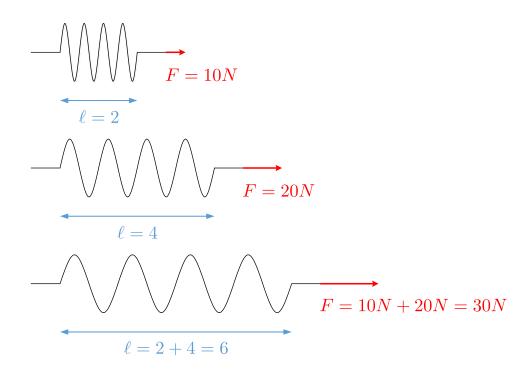

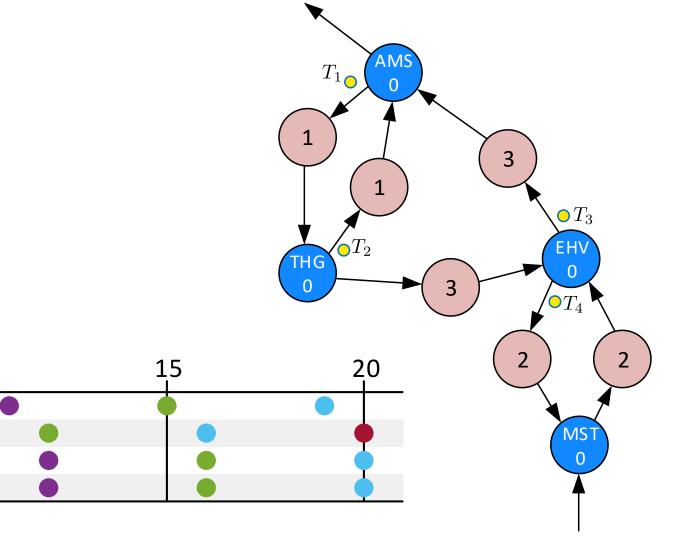

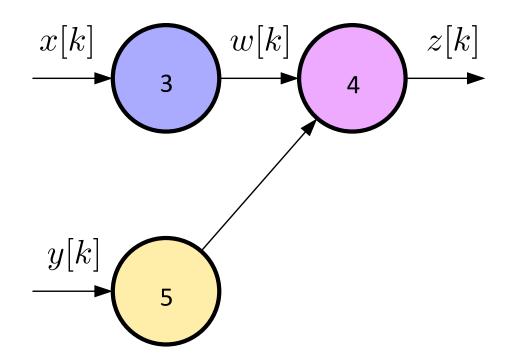

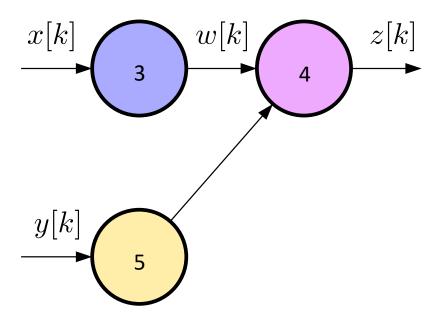

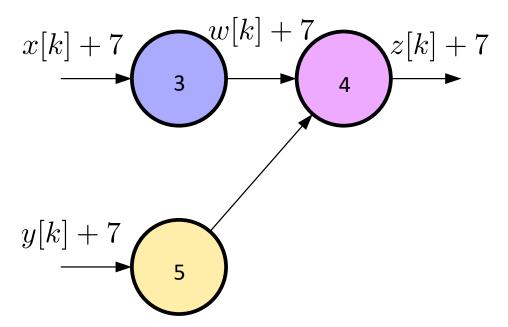

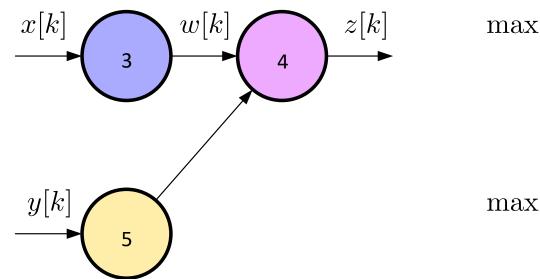

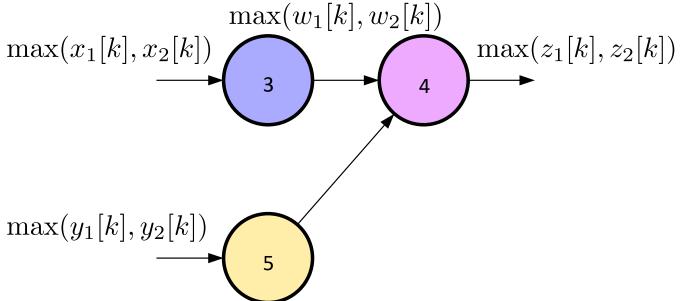

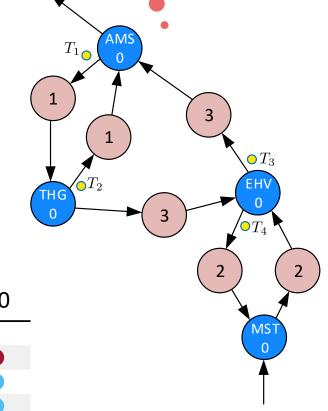

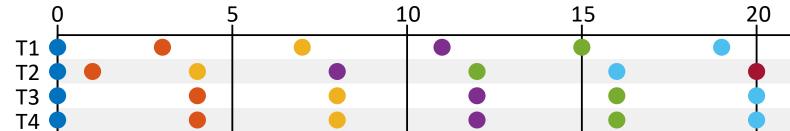

*Marc Geilen, Mladen Skelin, Hadi Alizadeh, Bram van der Sanden, João Bastos*, Max plus linear models for cyber-physical systems, 326

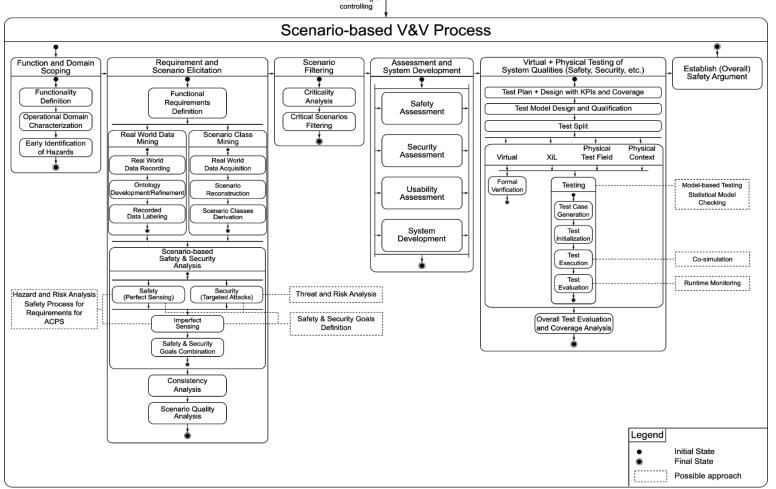

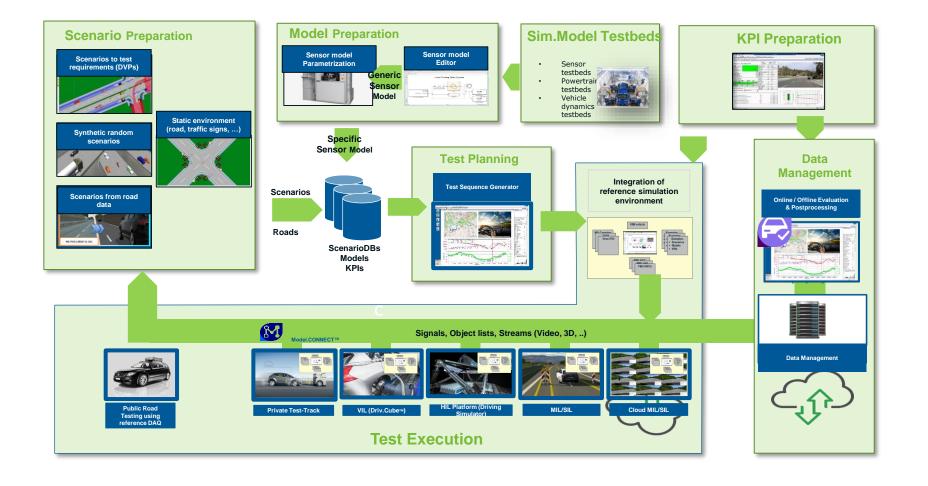

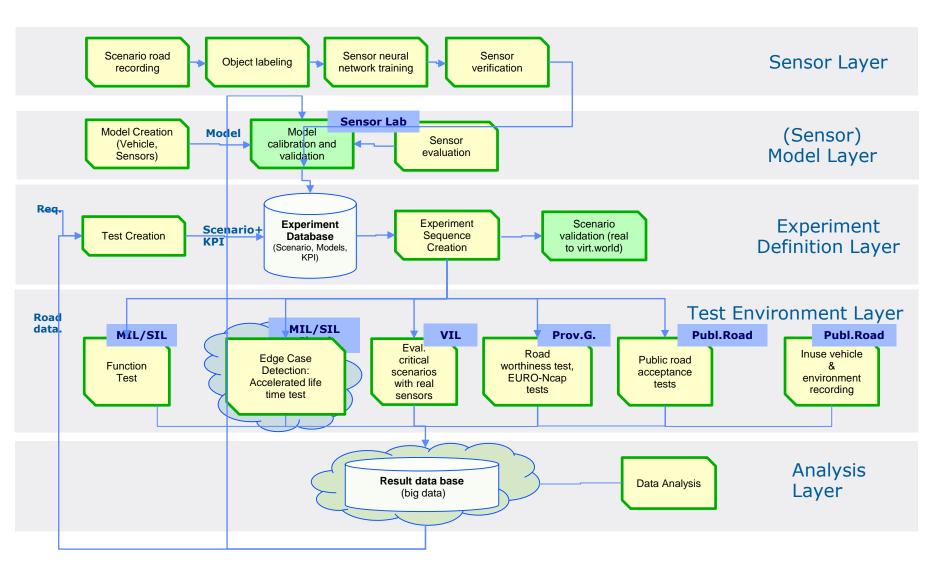

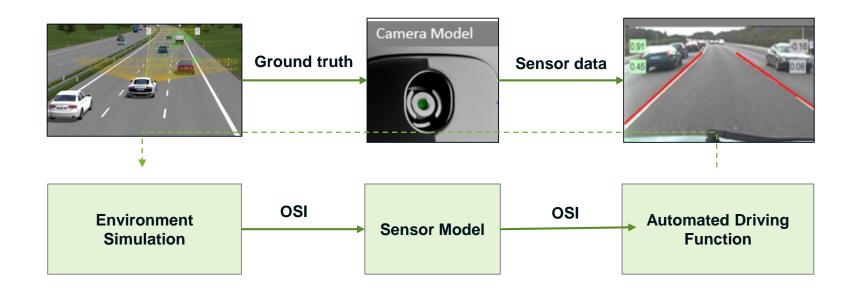

Michael Paulweber and Andrea Leitner, Comprehensive modular V&v framework for automated cyber-physical systems, 372

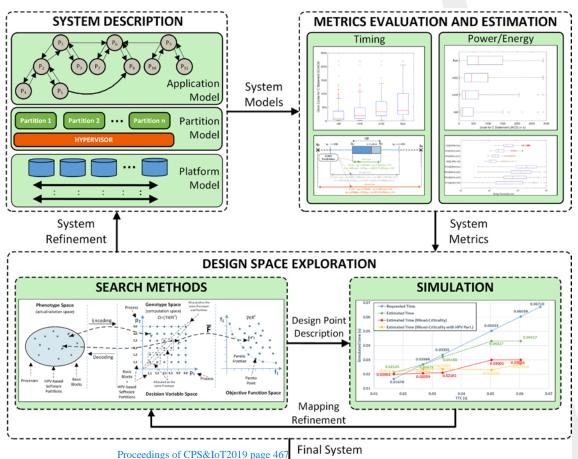

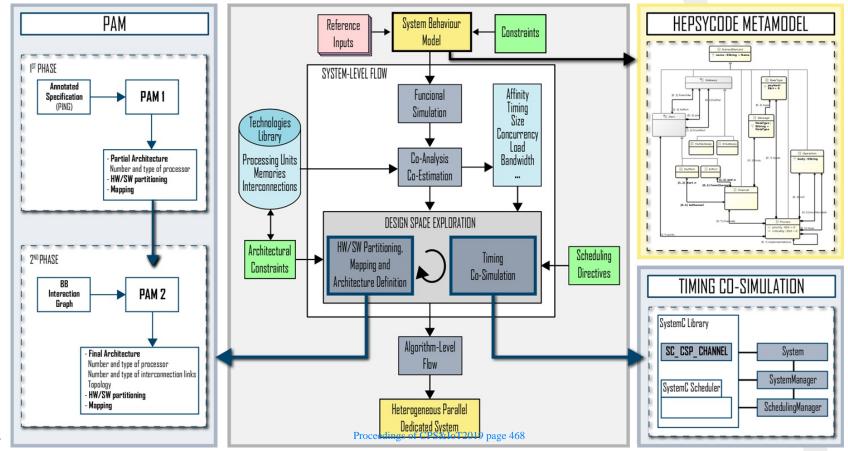

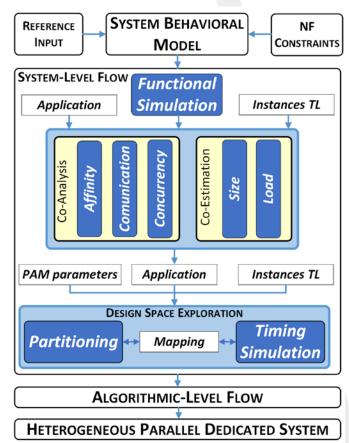

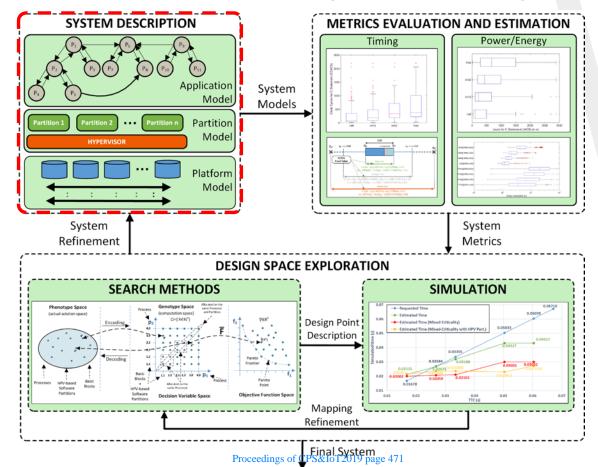

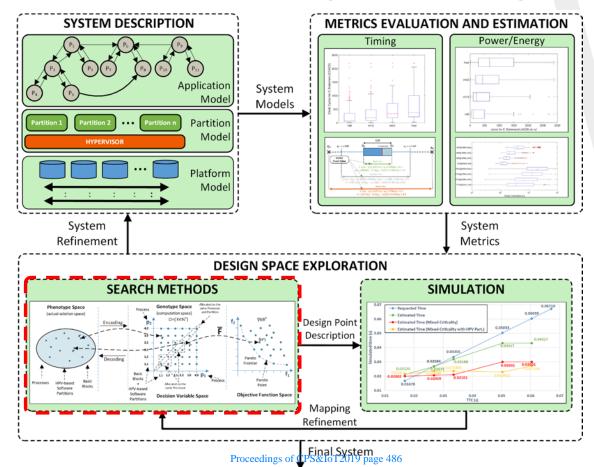

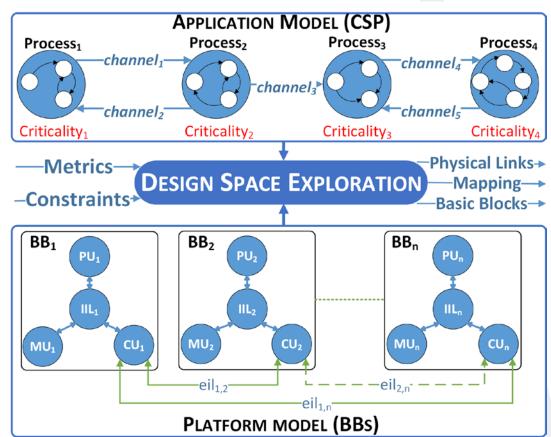

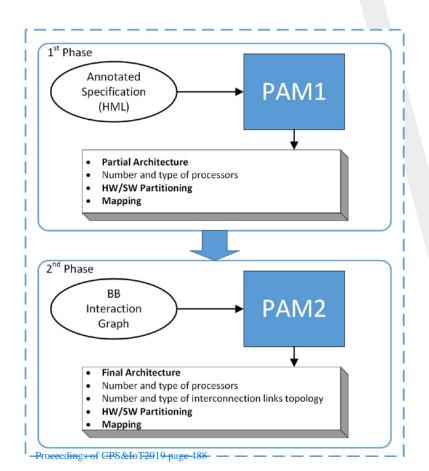

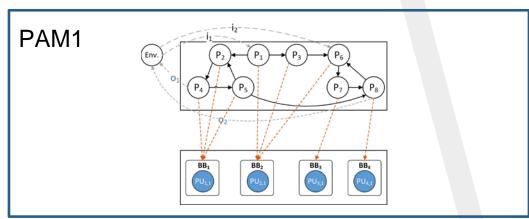

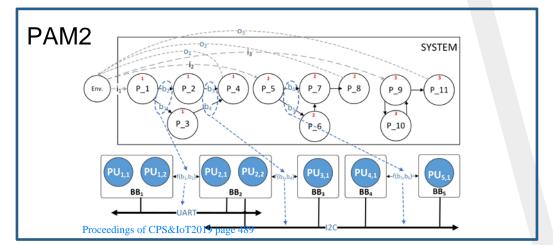

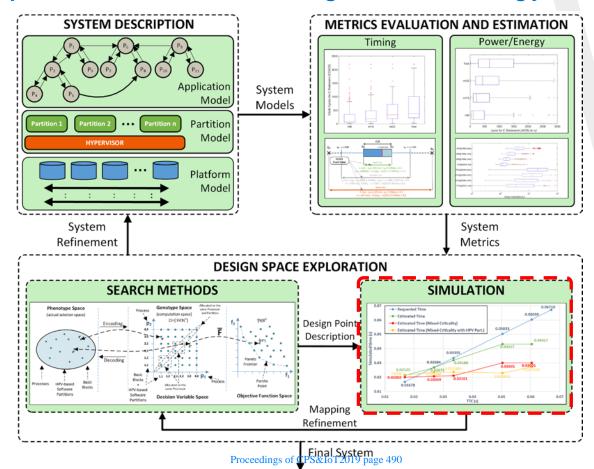

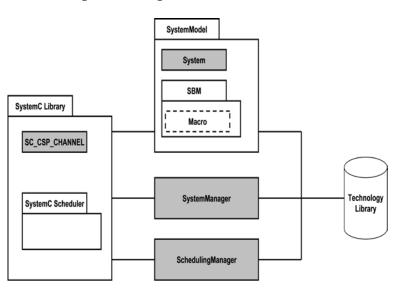

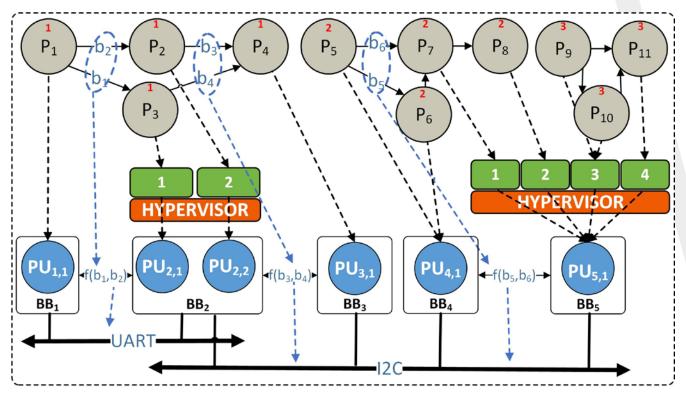

*Vittoriano Muttillo, Luigi Pomante*, Design space exploration for Hypervisor-based mixed-criticality systems, 435

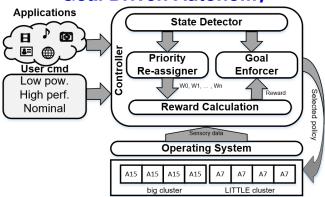

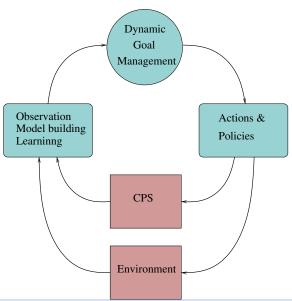

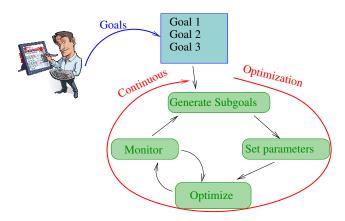

Axel Jantsch, Self-aware CPS, 517

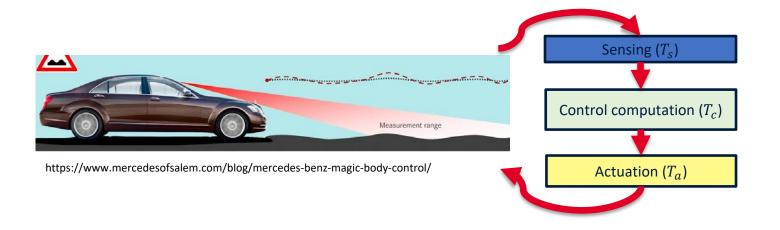

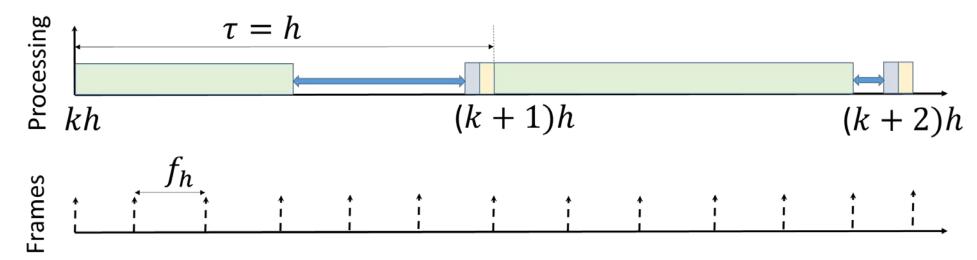

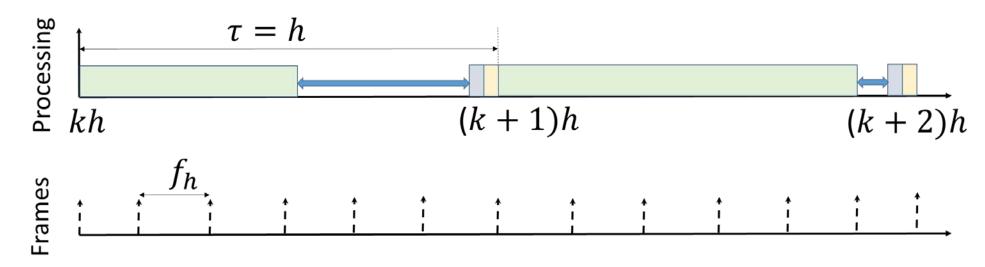

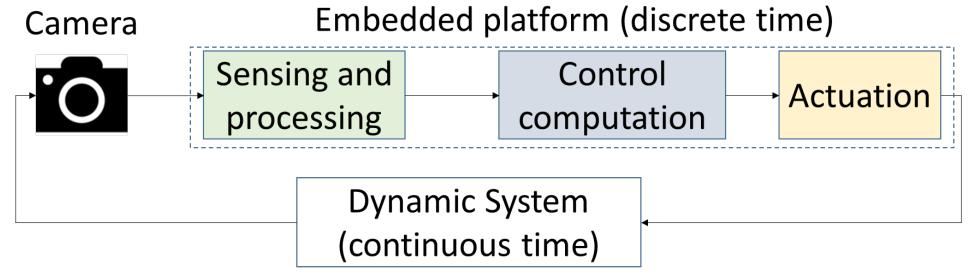

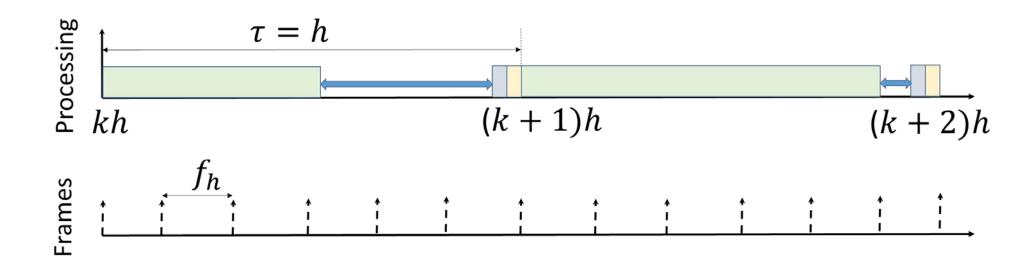

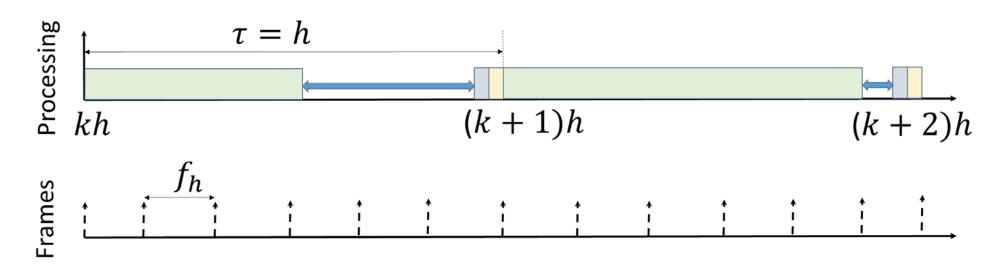

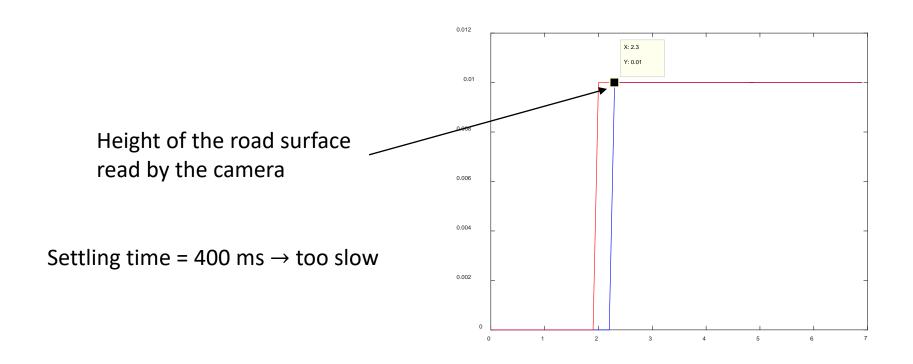

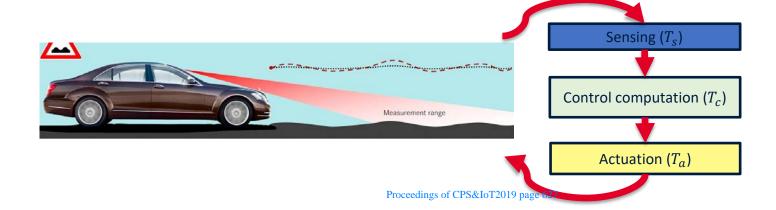

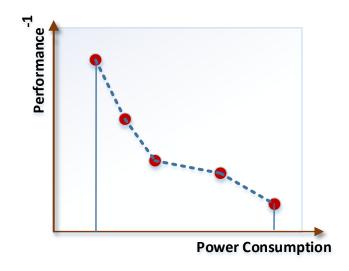

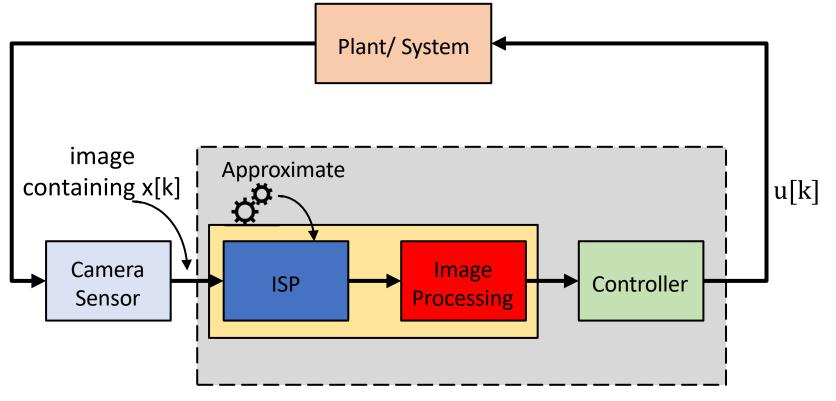

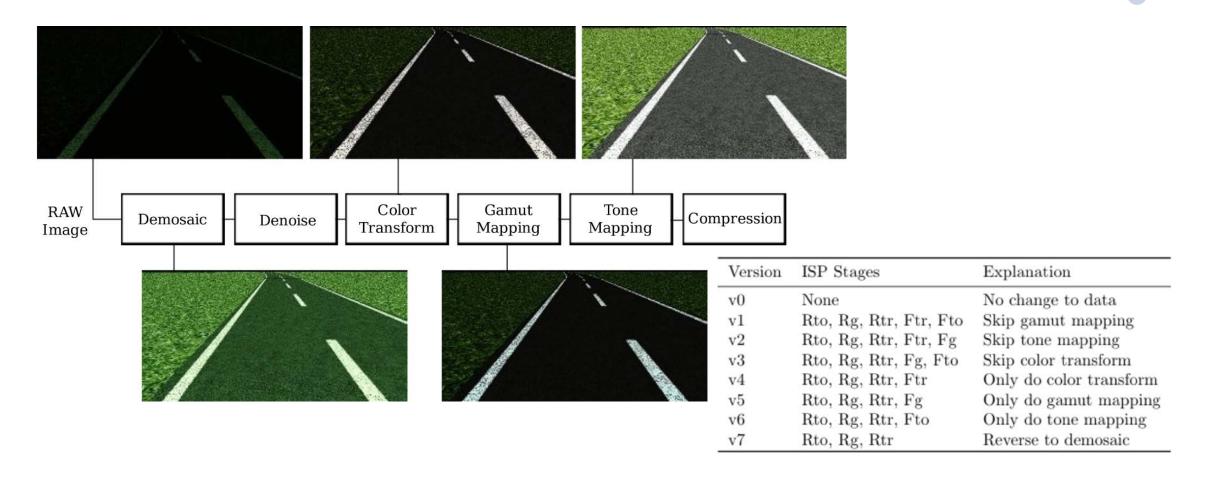

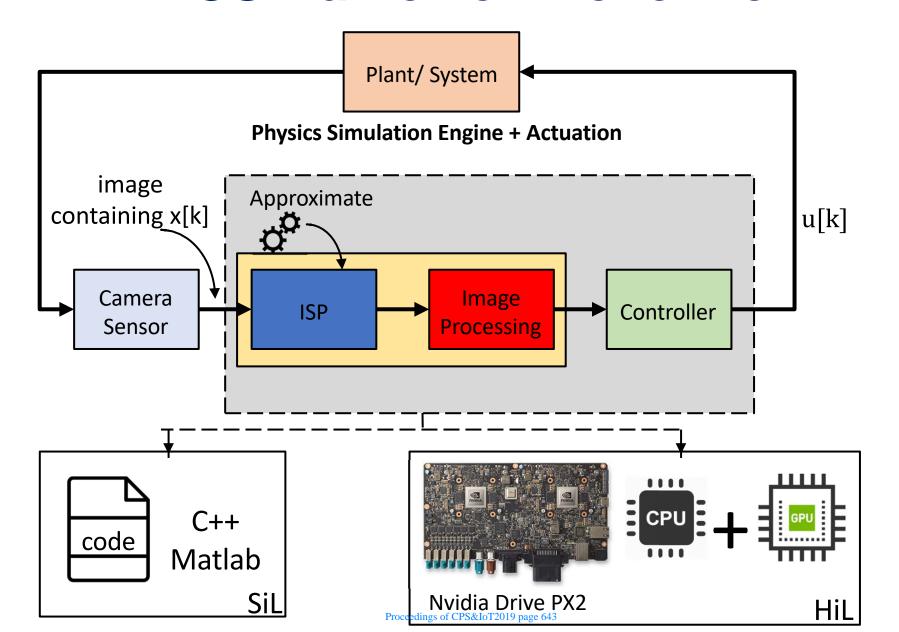

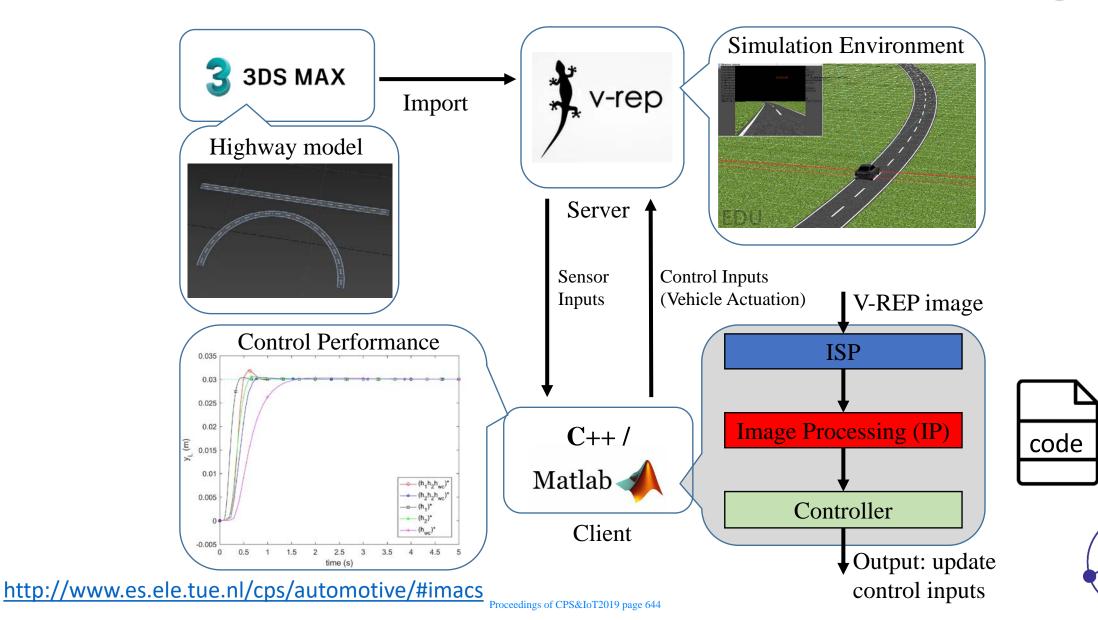

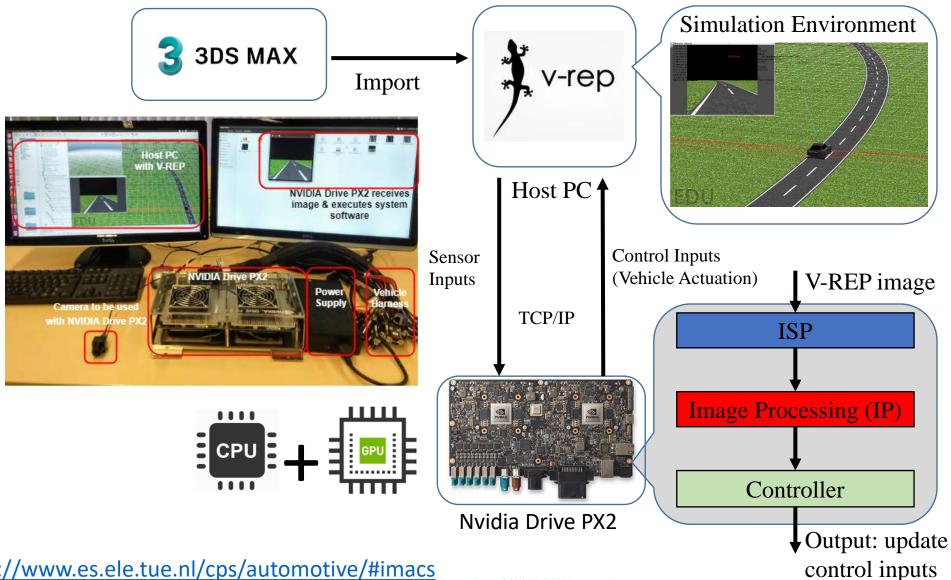

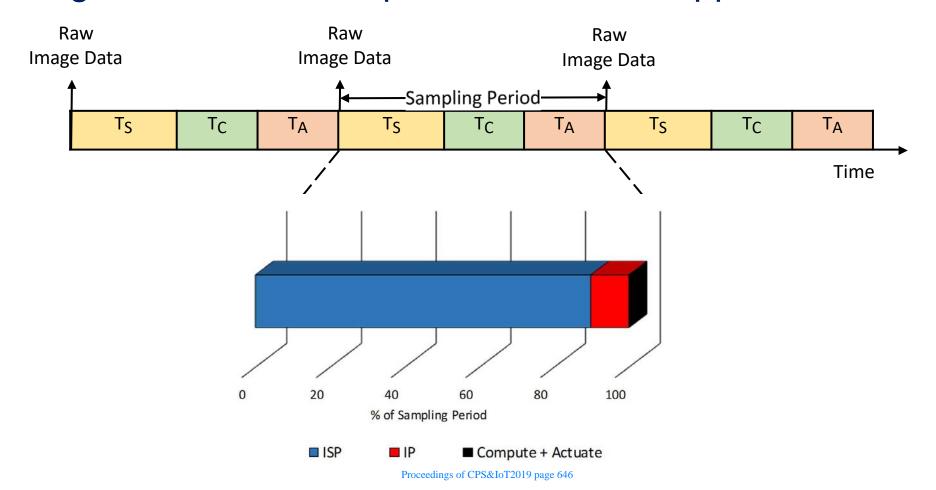

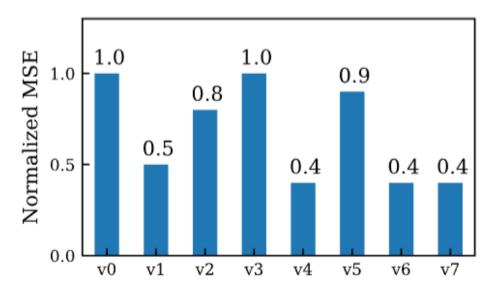

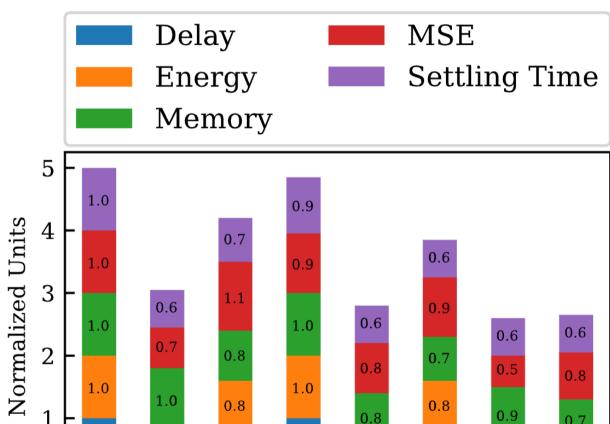

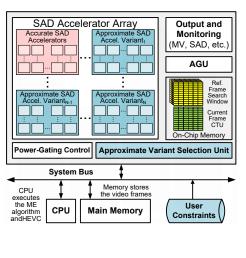

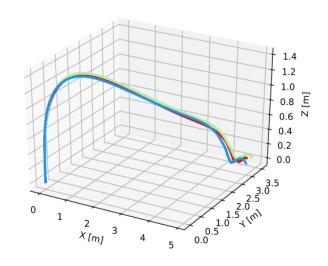

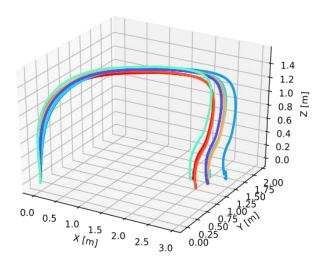

*Dip Goswami, Sajid Mohamed, Sayandip De*, Tradeoff analysis between Quality-of-Control and degree of approximate computing for image based control systems, 622

Radek Fujdiak, Security of Embedded and Cyber Physical Systems, 652

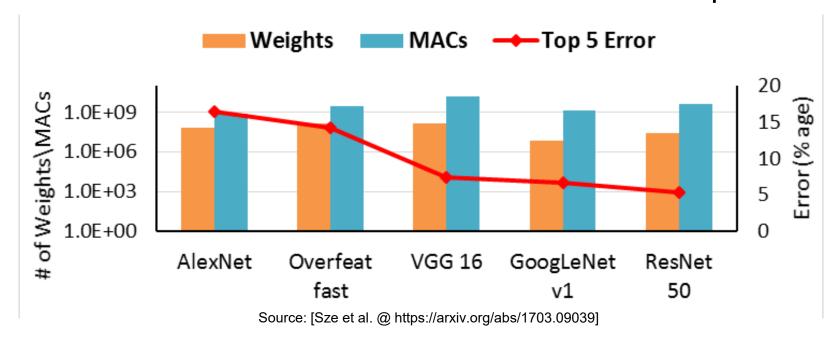

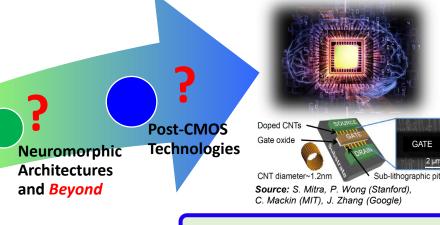

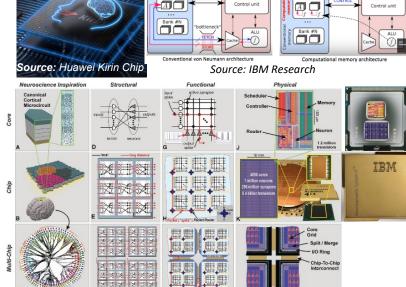

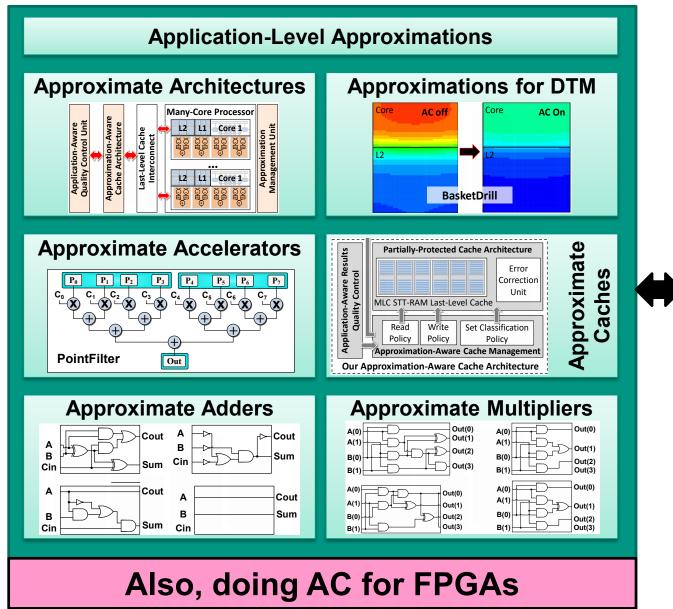

Muhamed Shafique, Brain-Inspired Computing for Smart CPS and IoT, 677

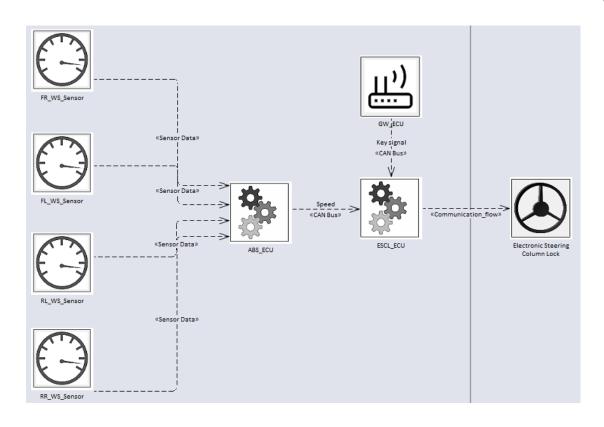

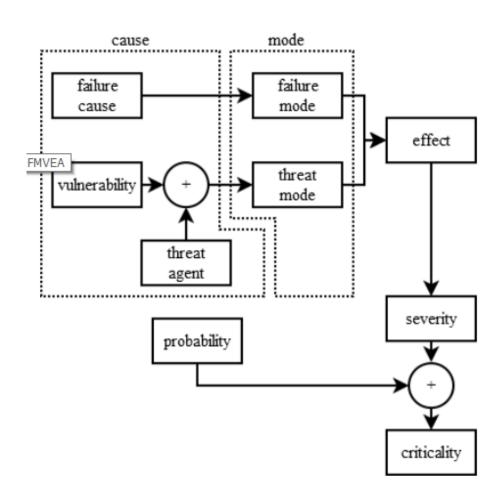

Christoph Schmittner and Thomas Gruber, Safety & security engineering of automotive CPS, 744

Lorenzo Strigini and Peter Popov, Probabilistic modelling integrating concerns of safety, security, etc., 793

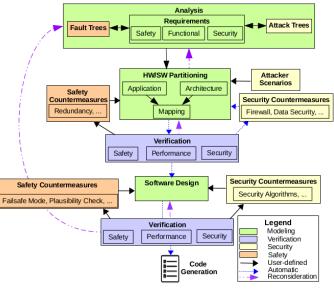

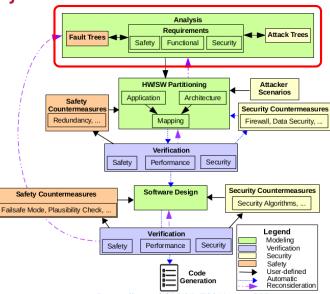

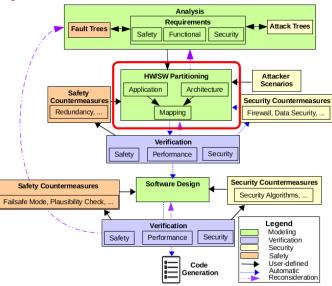

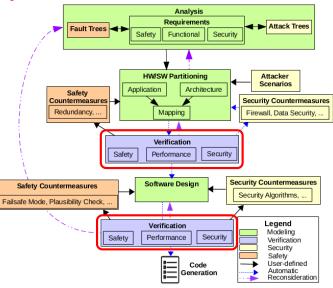

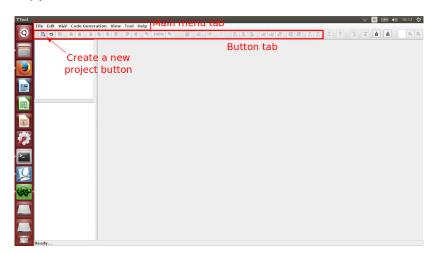

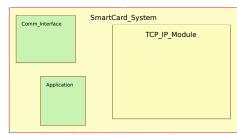

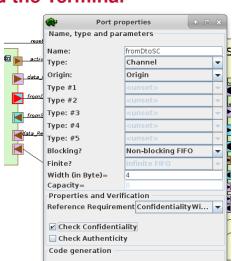

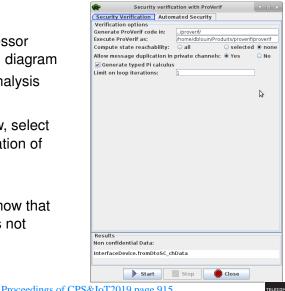

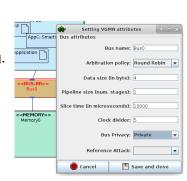

*Dominique Blouin, Maysam Zoor and Ludovic Apvrille*, Practical Embedded Systems Modeling and Safety, Security and Performance Verification with TTool, 846

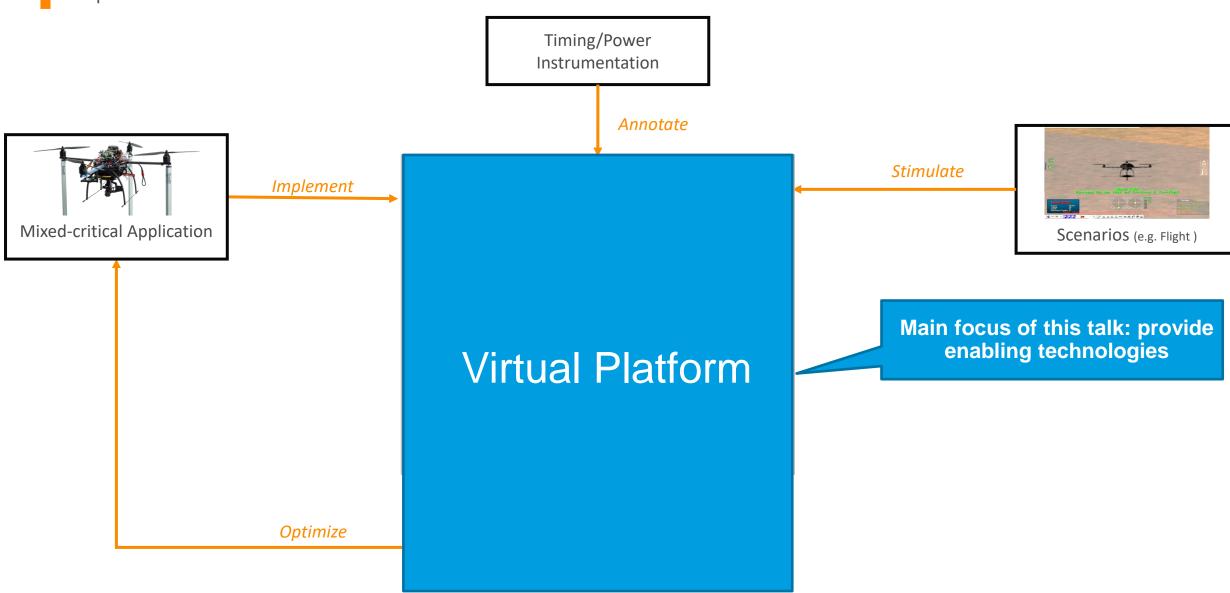

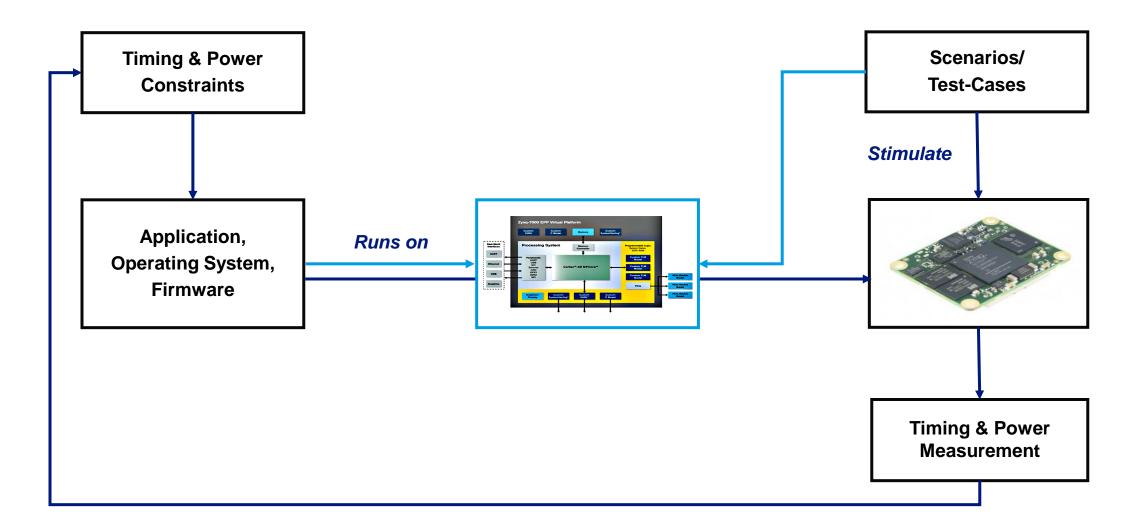

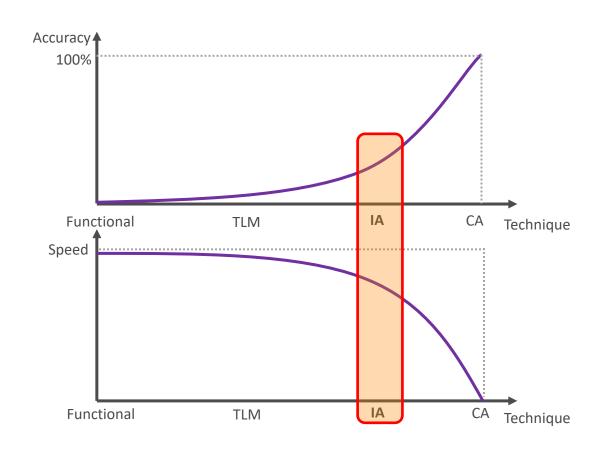

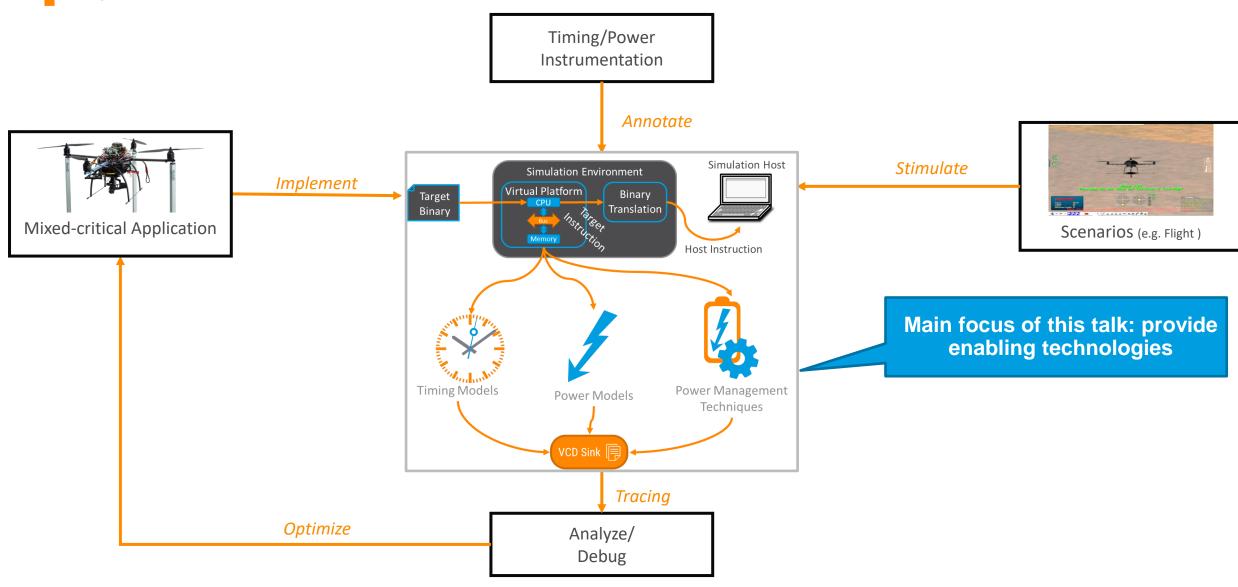

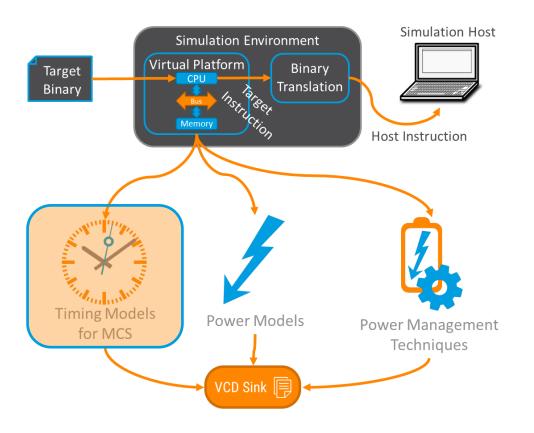

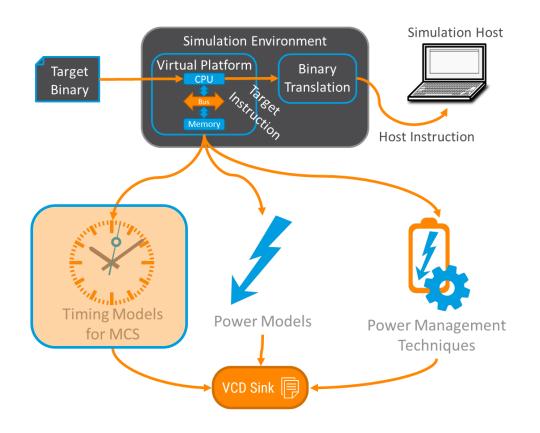

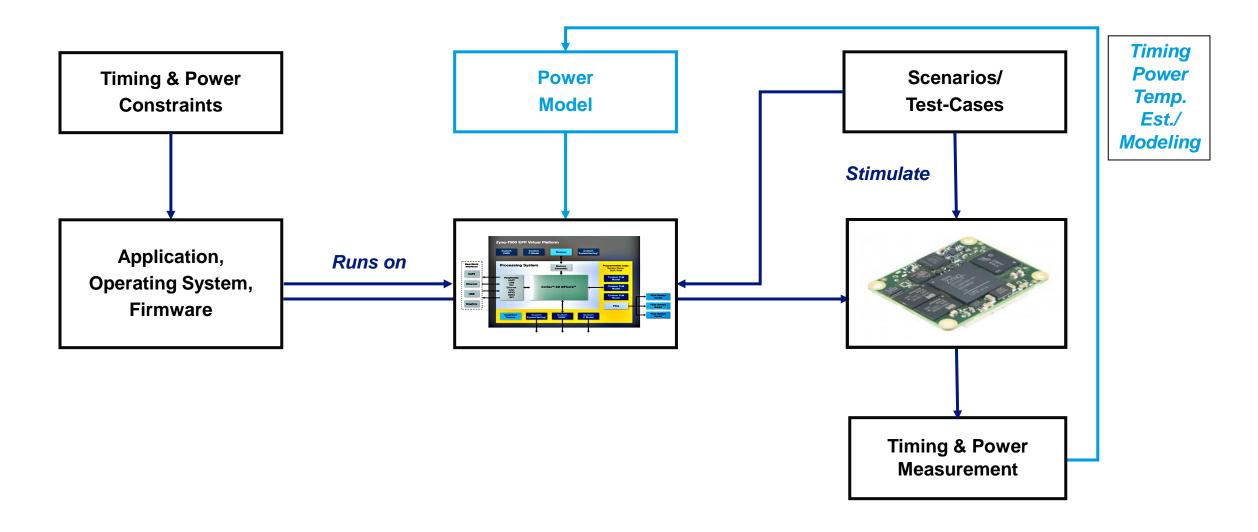

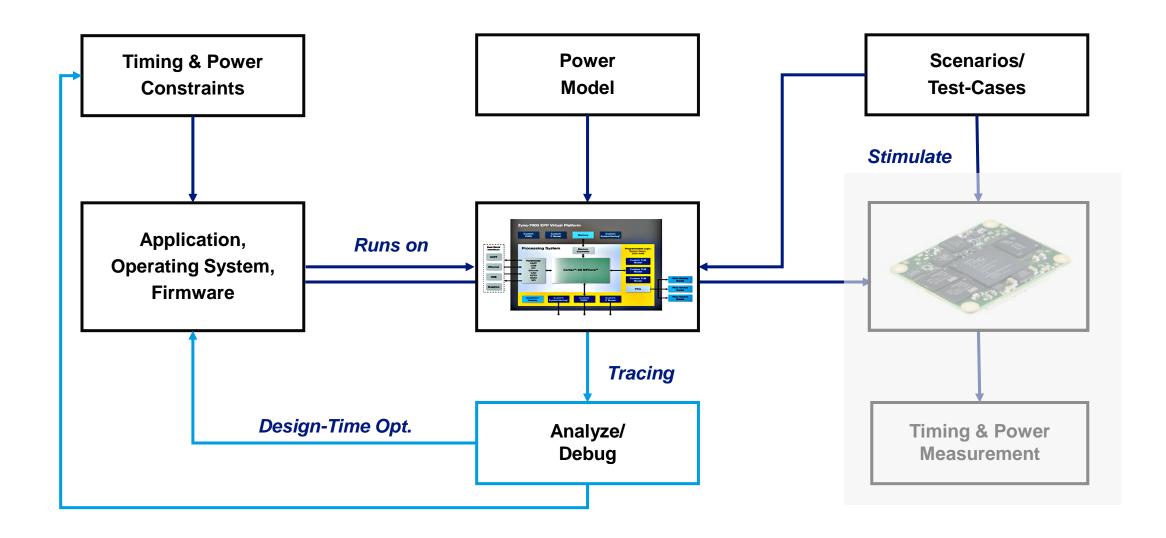

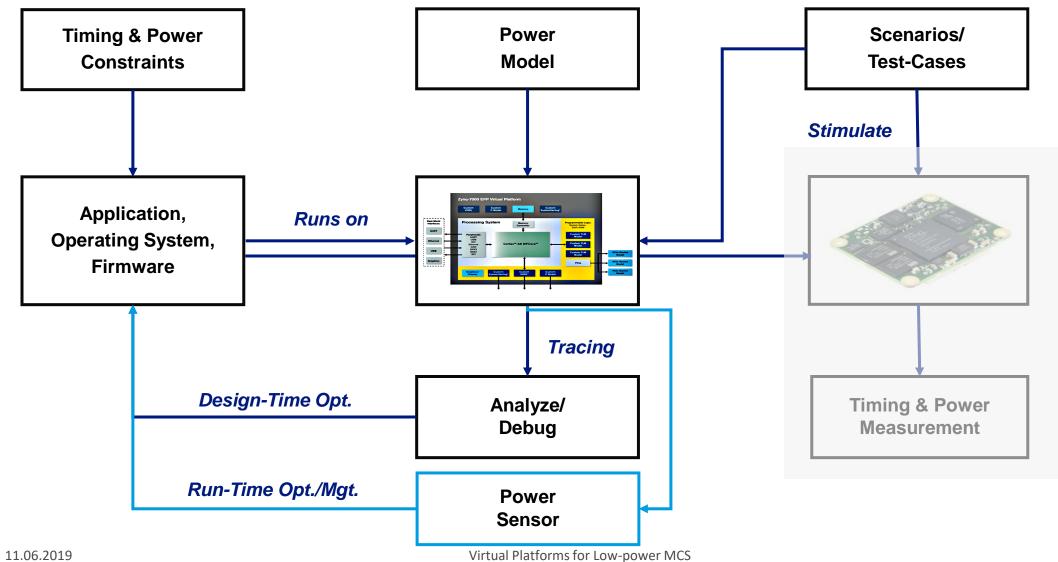

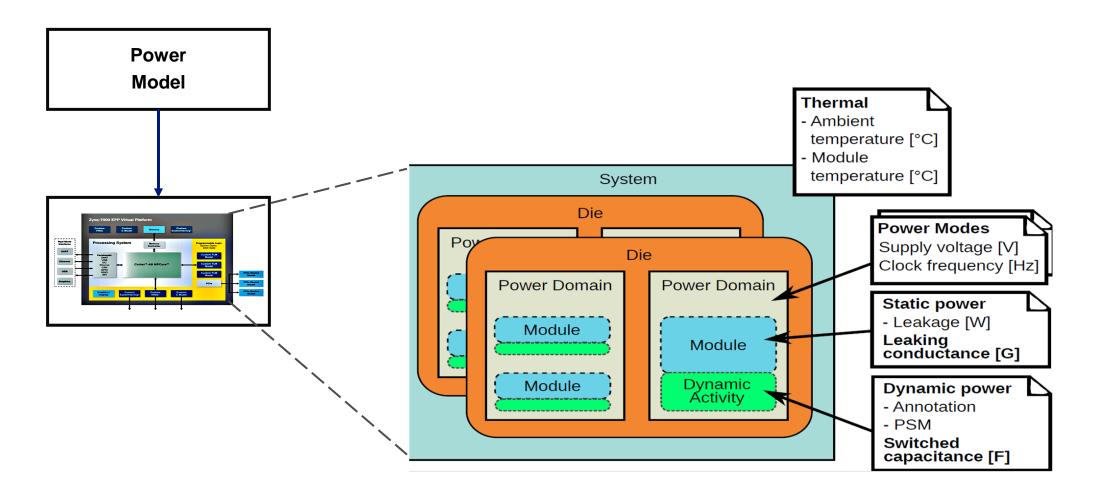

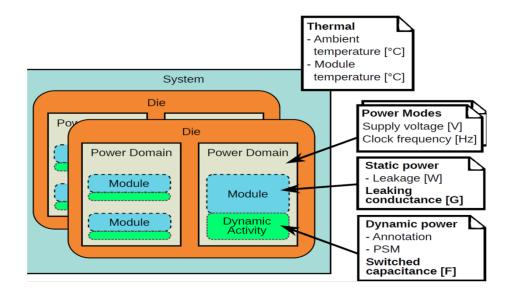

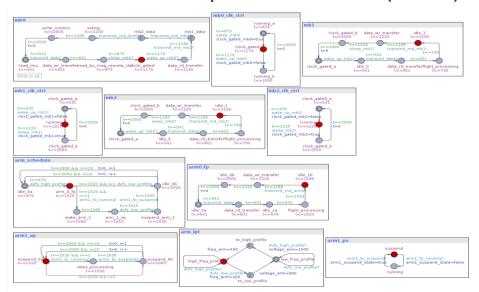

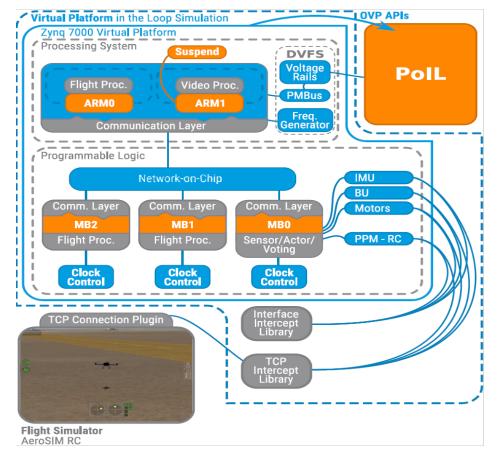

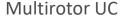

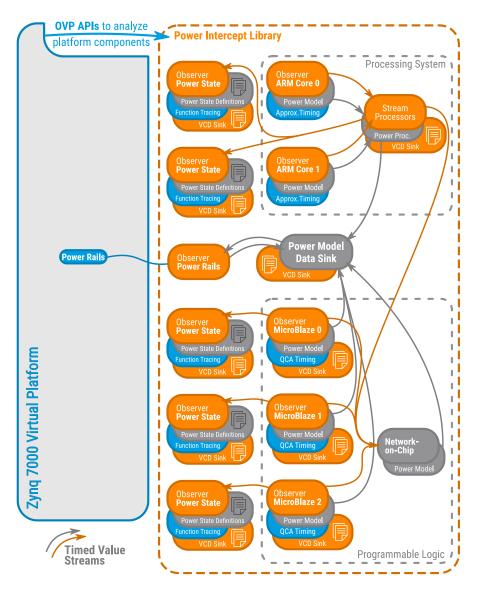

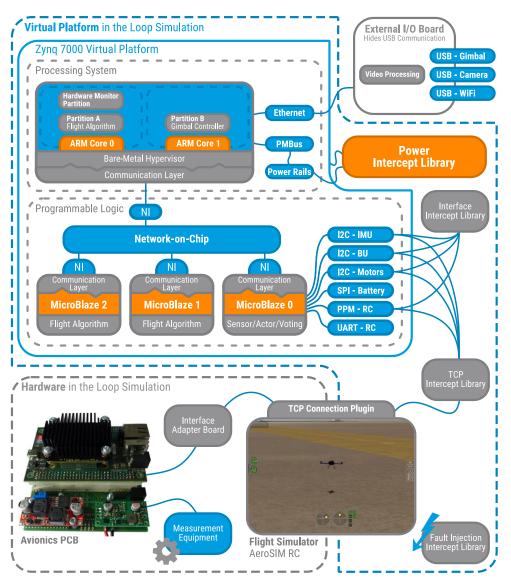

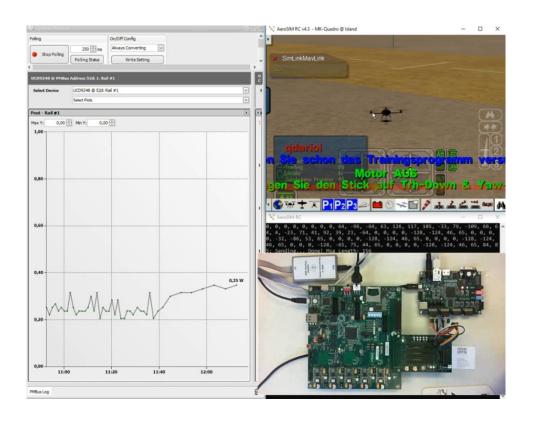

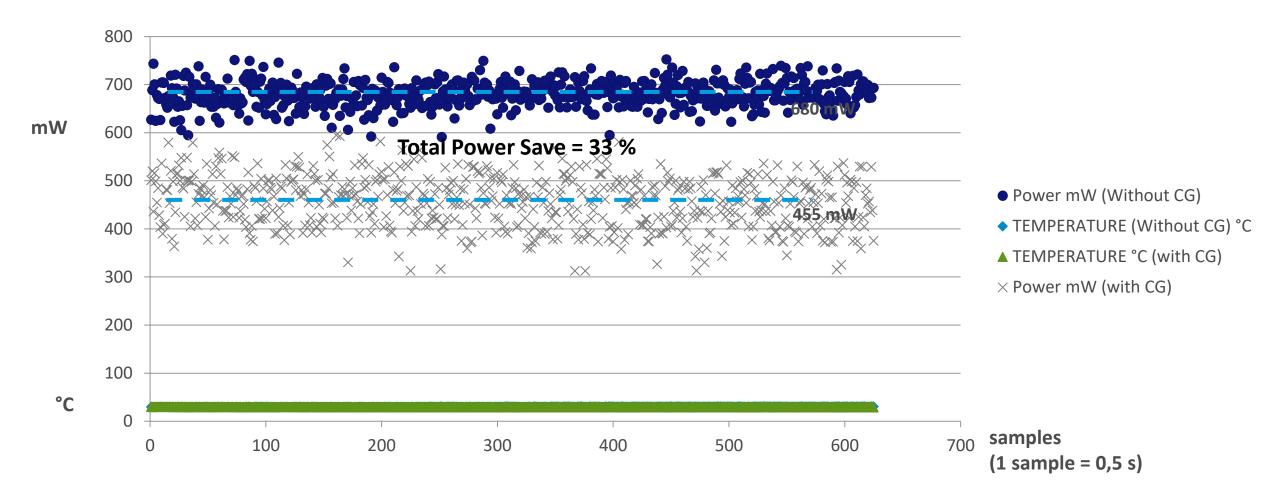

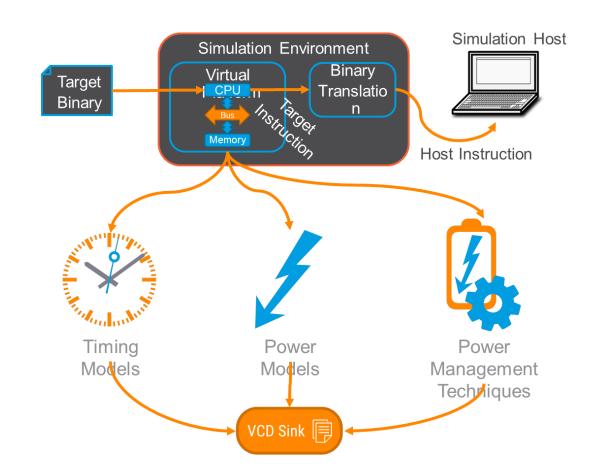

Razi Seyyedi, Sören Schreiner Virtual Platforms for Low-power Mixed-criticality Embedded Systems Development and Validation 940

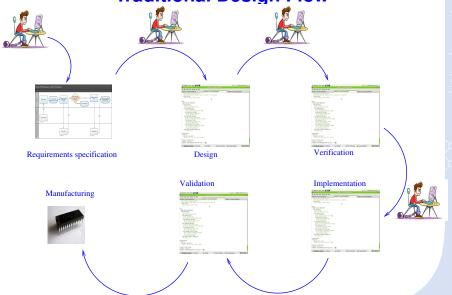

## Introduction to Modern Cyber-Physical Systems and their Quality-Driven Design

### **Outline**

- 1. Introduction

- 2. Modern cyber-physical systems (CPS)

- 3. Challenges of advanced CPS development

- 4. Computing technology for advanced CPS

- 5. Quality-driven design of advanced CPS

- 6. Conclusion

### **Introduction**: Aim of this tutorial

- □ The main aim of this tutorial is to prepare the ground for the whole CPS&IoT'2019 Summer School

- This means in particular:

- to introduce several basic definitions related to CPS

- to sketch the CPS scene, what includes:

- introduction to modern cyber-physical systems, their importance, their ongoing revolution, and challenges of their development, and

- explanation of the necessity of their holistic multi-objective quality-driven design

- to introduce the methodology of quality-driven model-based system design

### **Introduction:** Further reading for this tutorial

- L. Jóźwiak: Advanced Mobile and Wearable Systems, Microprocessors and Microsystems, Elsevier, Vol. 50, May 2017, pp. 202–221

- L. Jóźwiak: Quality-driven Design in the System-on-a-Chip Era: Why and how?, Journal of Systems Architecture, vol. 47, no. 3-4, Apr. 2001, pp. 201-224

- L. Jóźwiak: Life-inspired Systems and Their Quality-driven Design, Lecture Notes in Computer Science, Vol. 3894, 2006, Springer, pp. 1-16

- Jóźwiak, L.; Lindwer, M.; Corvino, R.; Meloni, P.; Micconi, L.; Madsen, J.; Diken, E.; Gangadharan, D.; Jordans, R.; Pomata, S.; Pop, P.; Tuveri, G.; Raffo, L. and Notarangelo, G.: ASAM: Automatic Architecture Synthesis and Application Mapping, Microprocessors and Microsystems journal, Vol.37, No 8, pp. 1002-1019, 2013

- Jóźwiak, L. and Jan, Y.: Design of Massively Parallel Hardware Multi-Processors for Highly-Demanding Embedded Applications. Microprocessors and Microsystems, Volume 37, Issue 8, November 2013, pp. 1155–1172.

- L. Jóźwiak and S.-A. Ong: Quality-driven Model-based Architecture Synthesis for Real-time Embedded SoCs, Journal of Systems Architecture, Elsevier Science, Amsterdam, The Netherlands, ISSN 1383-7621, Vol. 54, No 3-4, March-April 2008, pp. 349-368

- Many other papers of myself and my former Ph.D. students; many of them referenced in the above papers

### **Introduction:** What is a system?

- A system is a complex whole composed of interrelated, interdependent and/or interacting items (parts or elements of a system) that are so intimately connected that they appear and operate as a single unit in relation to the external world (to other systems)

- □ Three basic types of systems:

- unorganized system a mechanical unsystematic conglomerate of objects

- organized system a systematic, relatively stable and law-governed composition of parts which properties cannot be reduced to the simple sum of the properties of its parts, but involve some new emerging properties resulting from complex composition of the parts' properties (e.g. a molecule, crystal, circuit, computer), and

- organic stem formed not as a composition of some ready-made parts, but being an integral whole with distinguishable parts that originate, develop and die together with the whole, and cannot preserve and demonstrate their complete quality without the whole (e.g. life organisms); the characteristic features of the organic systems are the self-development and self-reproduction

- In this presentation organized systems will be considered

### Introduction: System organization and structure

- □ The system organization (composition) appropriately:

- defines its parts

- arranges the parts in relation to each other and to the whole, and

- interconnects them to form the whole

- □ The term **system structure** designates the **parts of a system arranged into a proper relation and appropriately interconnected** according to a certain set of laws and/or rules in order to form a whole

- We will consider material systems

- Since matter is active and is in constant change, the material systems are in constant change, with only some relative and transient stability conditions

- Compositions of interrelated, interdependent or interacting single changes (transformations, actions) form processes

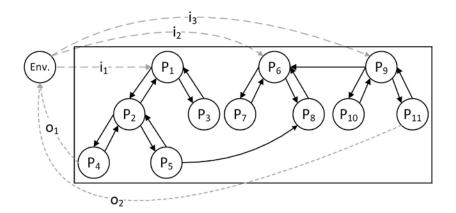

- Process is a relatively isolated composition of interrelated interdependent or interacting actions (transformations, changes)

Proceedings of CPS&LoT2019 page 6

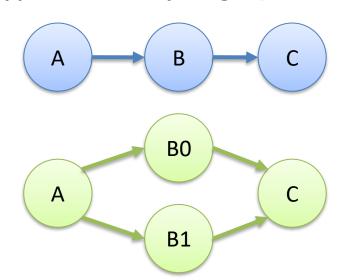

### **Introduction**: System = process © structure

- A given process can only perform (take place, occur) in particular relatively stabile conditions

- □ These conditions that make the process possible are created and guaranteed by the system **structure**

- □ The system structure is a relatively isolated, stable and slowly changing (in relation to the process) part of the universe in which a particular process (or a collection of co-operating processes) can take place

- □ A system is a unity of a process and structure in which this process takes place

- System design is an activity of defining an appropriate composition of the system process and structure

### **Introduction:** What are cyber-physical systems?

- Cyber comes from Greek adjective kyberneticos (cybernetic) that means skilled in steering or governing

- Already in ancient times people constructed various systems: the oldest known artificial automatically controlled system is probably a water clock invented by Ktesibios (285–222 BC) in Alexandria

- □ Form those times, the construction of machines (physical systems) and their controllers (cyber systems) continued and developed through the centuries

- Until the end of 19th century the controllers (cyber systems) were implemented as mechanical, hydraulic and pneumatic systems

- □ In the 20th century they started to be gradually replaced by the electric controllers, and later by the electronic controllers

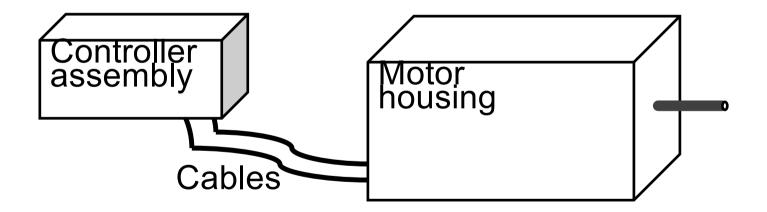

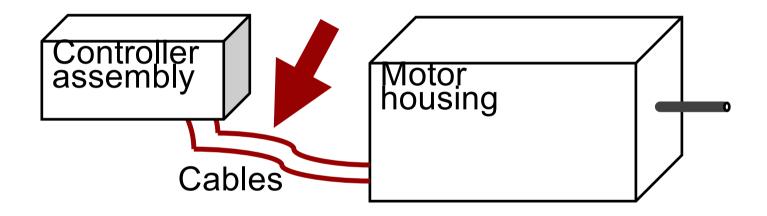

- Physical systems are systems in which matter or energy acquisition, processing and transfer take place according to the lows of physics

- Cyber systems are (parts of) control systems, i. e. information collecting, processing and communicating systems

### **Introduction**: What are cyber-physical systems?

- Cyber-physical system (CPS) is a compound system engineered through integration of cyber and physical sub-systems or components and/or preexisting component cyber-physical systems, so that it appears and operates as a single unit in relation to the external world (to other systems)

- Introduction of the transistor and integrated circuit technologies in the years 1950s and 1960s, correspondingly, enabled the *ongoing microelectronics* and information technology revolution that is till now progressing according to the Moore's low

- □ The revolutionary progress in computing platforms, communication, networking, sensors and actuators enables:

- much more effective and efficient CPS for traditional applications, and

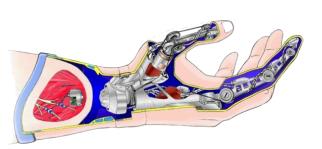

- "smart", sophisticated and affordable CPS for numerous new applications, e.g. smart robots, homes, cars, wearable and implantable medical devices, etc.

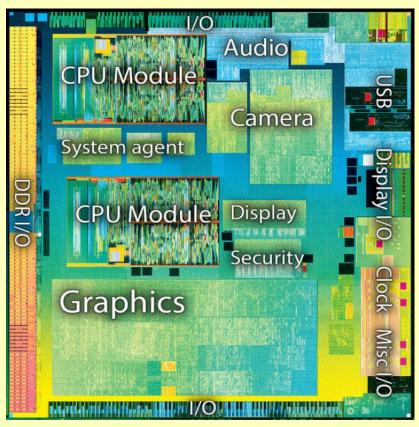

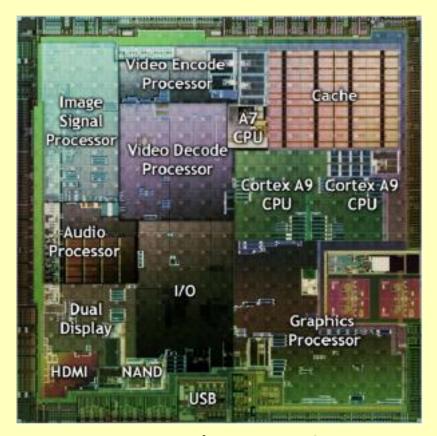

### Introduction: very complex MPSoCs

- Modern nano-dimension semiconductor technology enables implementation of a very complex multiprocessor system on a single chip (MPSoC)

- This facilitates a rapid progress in:

- global networking

- (mobile) wire-less communication

- (mobile autonomous) embedded computing

**NVIDIA Tegra K1** massively parallel MPSoC for mobile applications

CPU: (4+1) Cortex-A15 cores

Kepler GPU: 192 CUDA GPU cores

Source: ANANDTECH

(http://www.anandtech.com/show/7622/nvidia-tegra-k1)

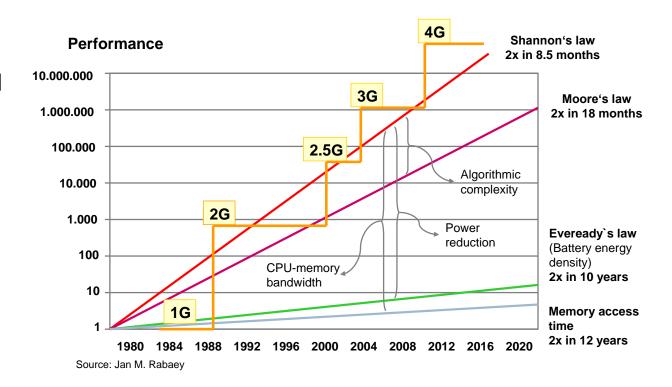

### Introduction: cyber-physical technology revolution

### The recent rapid developments in:

- system-on-a-chip technology

- common global networking

- wire-less communication

- mobile and autonomous computing

- miniaturized sensors and actuators

- material technology

## created a large discrepancy between what is possible and what is used nowadays

- This discrepancy:

- causes both a very strong technology push and market pull to create new or modified products and services, and

- results in the cyber-physical technology revolution

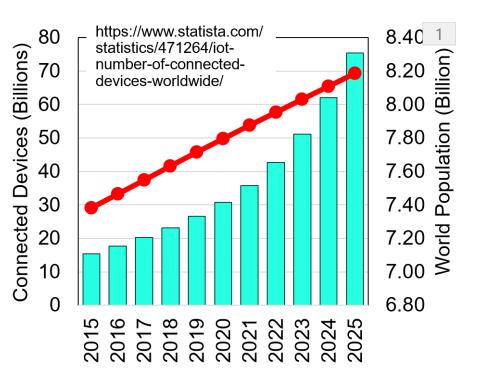

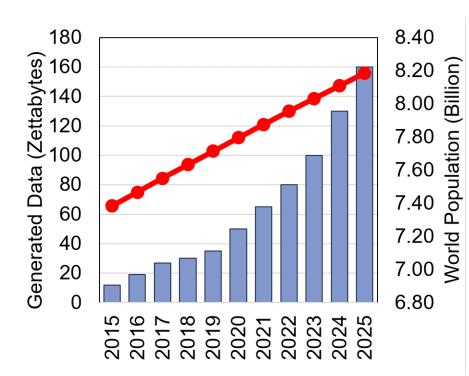

- Recently, a revolutionary transition has been started from the internet of computers to the internet of smart (mobile) cyber-physical systems (CPS), called Internet of Things (IoT)

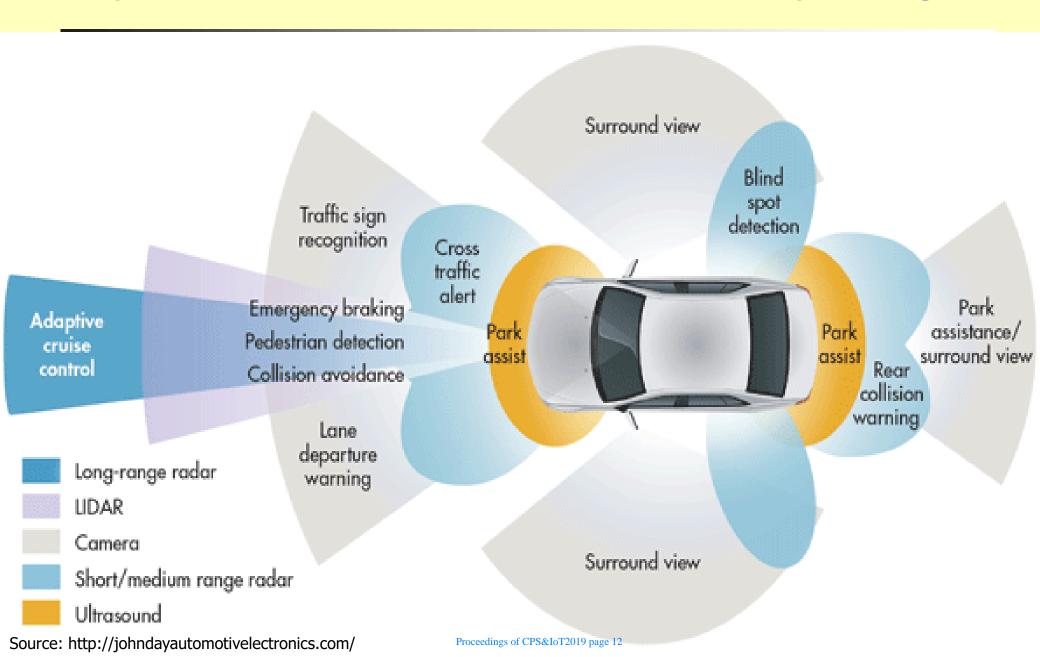

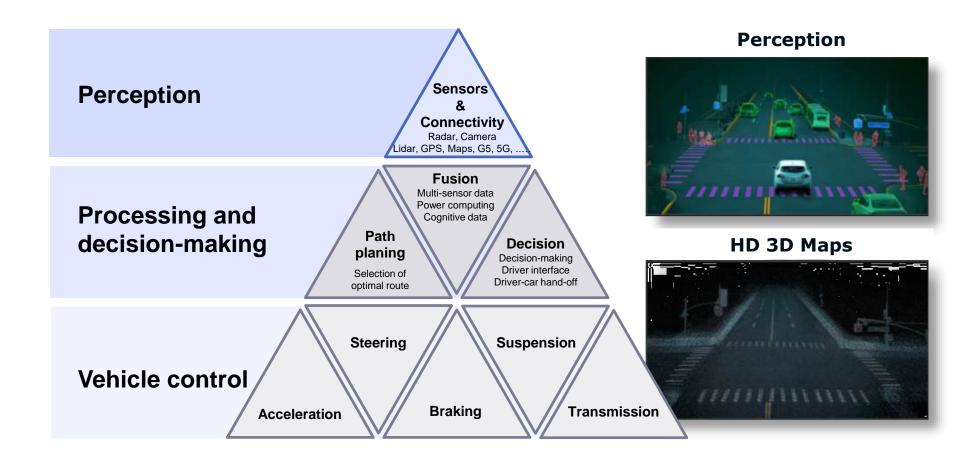

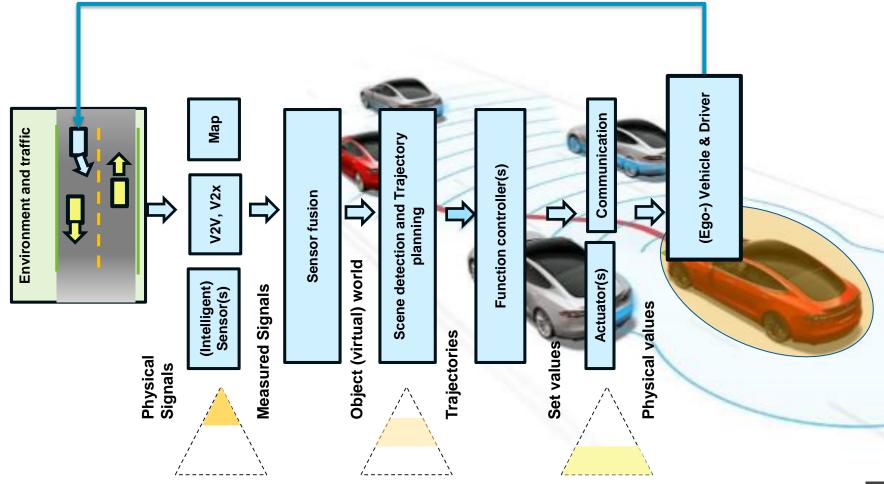

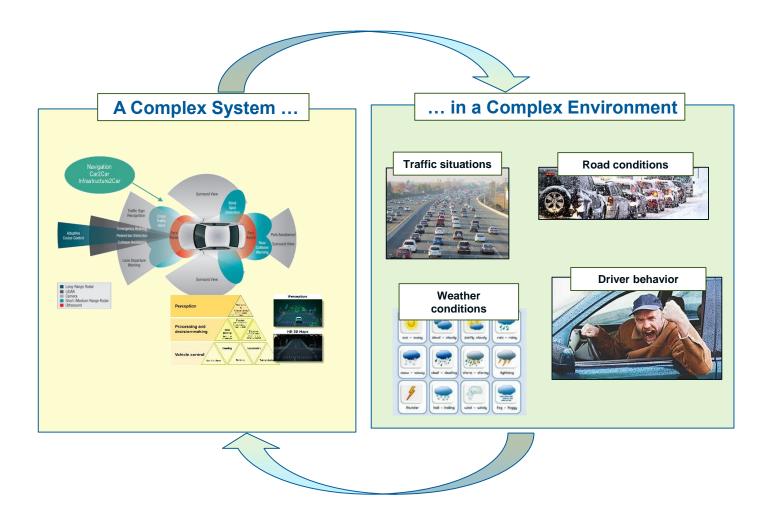

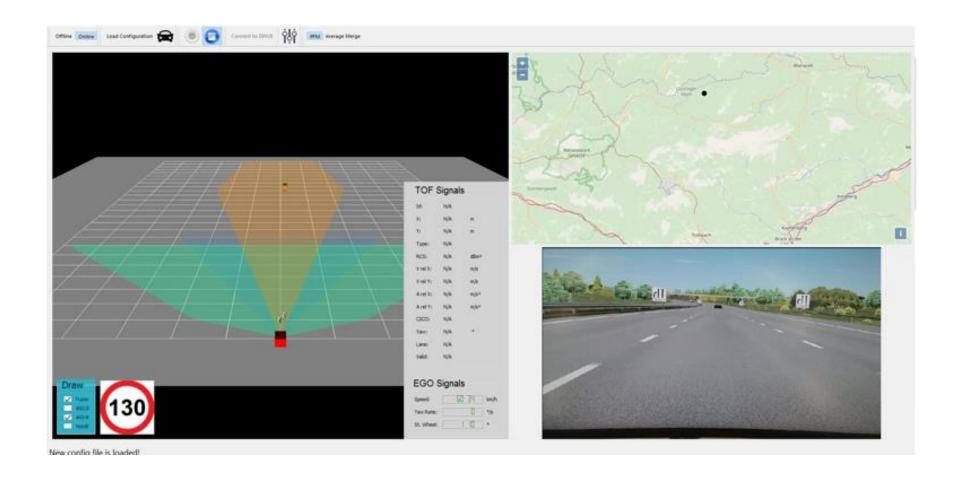

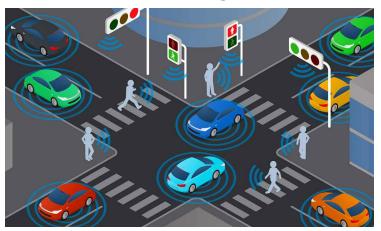

### Examples of modern mobile CPS: autonomously-driving cars

## Examples of modern mobile CPS: smart wearables

## Examples of CPS: wearable virtual and augmented reality

Source: http://www.technodo.com/

14

# Examples of modern CPS: smart miniaturized implants and pill-size medical devices

modern 10 times smaller pace-makers

A new wave of the information technology revolution has arrived that creates much more coherent and fit to use CPS and connects them to form the IoT

### Importance of modern mobile CPS

- Application areas of mobile CPS cover virtually all socially important application sectors, including:

- consummer applications, e.g. mobile computing, communication, localization, navigation, gaming, entertainment, fashion, etc.

- extension or replacement of human capabilities, e.g. tele-operation, personal assistance, artificial limbs, implants, etc.

- social systems, e.g. smart health-care and other numerous health-care applications, assisted leaving, law enforcement, public safety, military, etc.

- transportation and automotive, e.g. traffic control, navigation, tracking, communication, mobile fares and personalized customer service, assisted/autonomous driving, etc.

- *industrial, safety, security and military applications*, e.g. mobile real-time in-the-field surveillance, monitoring, inspection, repair, robotics, instruction, assistance, etc.

- commercial applications, e.g. mobile inventory tracking and customer service, wearable augmented reality and other systems for touristic applications, and many others

- □ The economic and societal importance of mobile CPS is very high and rapidly increases

16

### Rapid growth of the mobile CPS and IoT markets

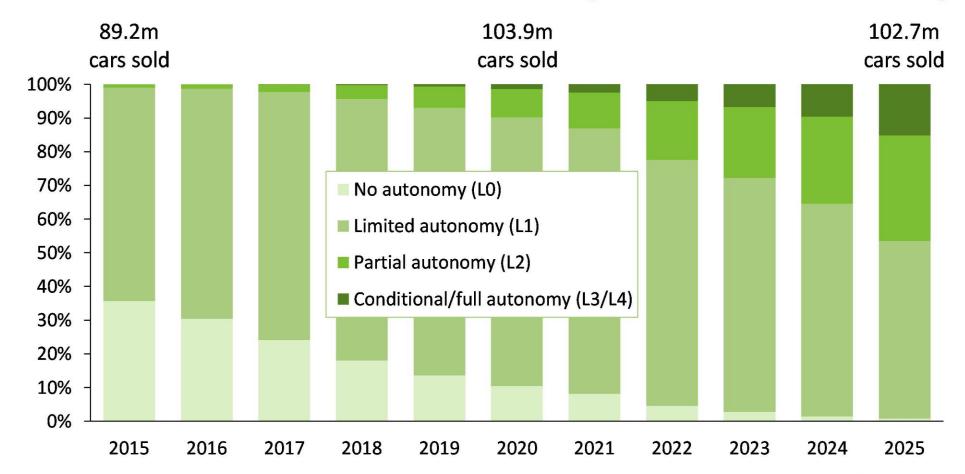

## Worldwide car sales forecast by level of autonomy

Source: Canalys estimates, Autonomous Vehicle Analysis, December 2016

canalys

### Rapid growth of the mobile CPS and IoT markets

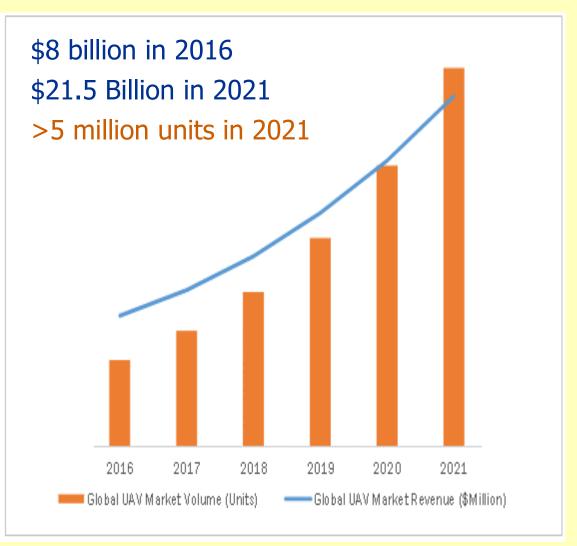

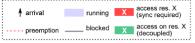

### Global unmanned aerial vehicle (UAV) market

- The fastest growing market of all mobile sectors is this of smart wearable devices:

- \$14 billion and 123 million devices in 2016

- \$34 billion and 411 million devices in 2020

(CCS Insight, February 2016)

Source: BIS Research, January 2018

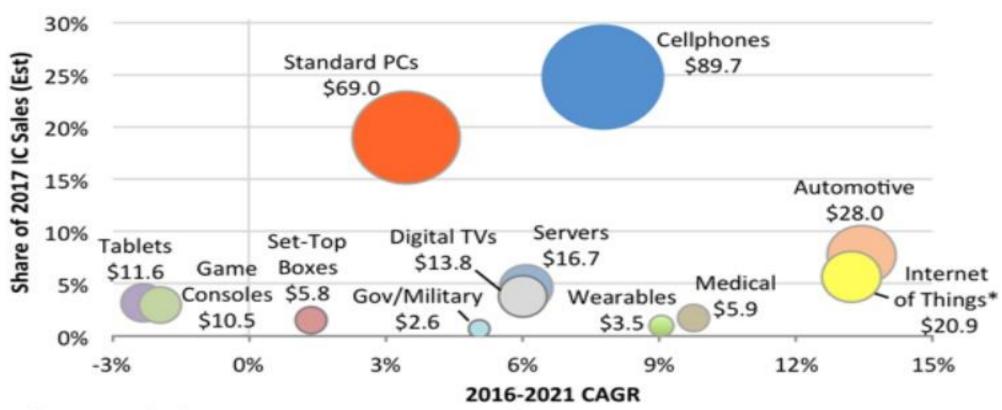

### Rapid growth of the **chip market** for mobile CPS and IoT

### IC End-Use Markets (\$B) and Growth Rates

<sup>\*</sup>Covers only the Internet connection portion of systems.

Source: IC Insights

Source: IC Insights

☐ The fastest-growing chip markets are automotive, IoT, medical and wearables

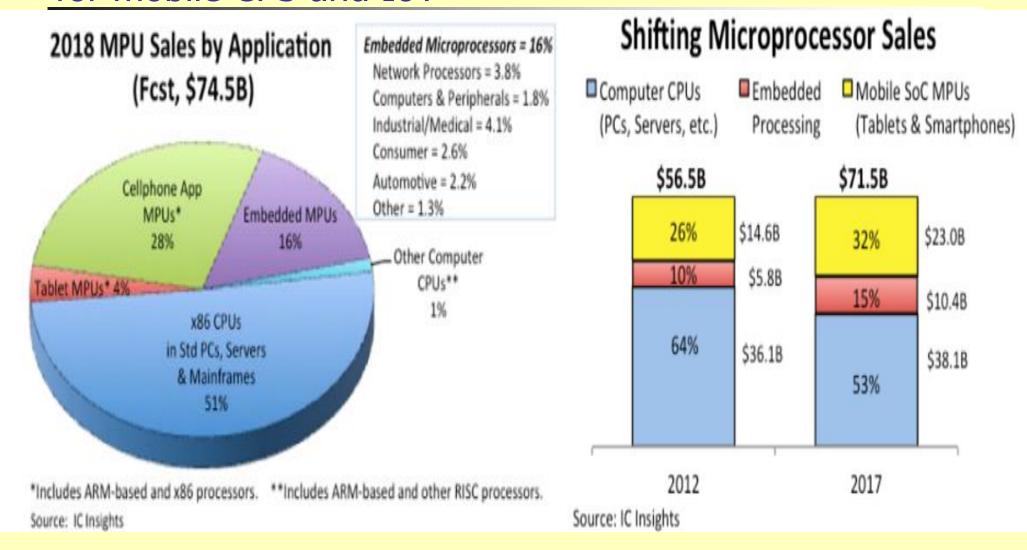

## Rapid growth of the **processor and MPSoC market** for mobile CPS and IoT

<sup>■</sup> MPUs for mobile systems account for almost 50% of MPU sales, and this share repidly increases

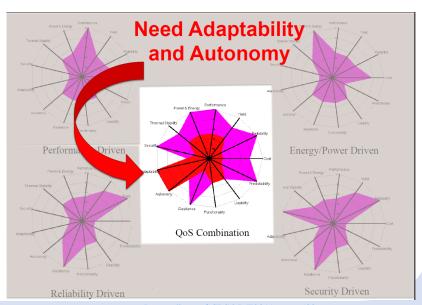

### Challenges: unusual complexity and ultra-high demands

- The huge and rapidly developing markets of sophisticated mobile CPS represent great opportunities

- These opportunities come with a price of:

- unusual system complexity and heterogeneity, resulting from convergence and combination of various applications and technologies in one system or even on one chip, and

- stringent and difficult to satisfy requirements of modern applications

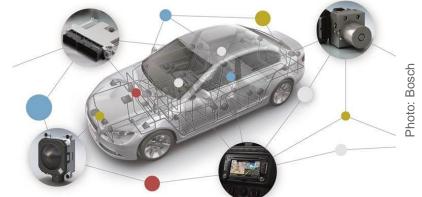

- Smart cars, drones and various wearable systems:

- involve big instant data from multiple complex sensors (e.g. camera, radar, lidar, ultrasonic, sensor network tissues, etc.) and from other systems, used for mobile vision, imaging, virtual or augmented reality, etc.

- are required to provide continuous autonomous service in a long time

- are safety-critical

- In consequence, they demand a guaranteed (ultra-)high performance and/or (ultra-)low energy consumption, while requiring a high reliability, safety and security

Proceedings of CPS&IoT2019 page 21

21

# **Challenges**: distribution of intelligence, computing resources, services and workloads in the IoT chierarchy

- To transform the big data from multiple sensors to the information being directly used for decisions, while satisfying the stringent requirements of the modern mobile systems, a careful distribution of information delivery and computation services among the different layers of IoT is needed

- For many reasons of primary importance, as:

- real-time availability of local information

- guaranteed real-time reaction

- security, safety, reliability

- minimization of communication traffic and energy, etc.

a majority of computing and decision making related to advanced CPS should be performed locally in the IoT edge devices, in collaboration among various local IoT edge devices or just above the edge nodes, and not in the higher levels of fog or in cloud

- □ The higher levels of fog and cloud should only be asked for services if:

- necessary information or computing resources are not available locally, and

- reaction-time, security, safety, etc. allow for this

# **Challenges**: distribution of intelligence, computing resources, services and workloads in the IoT chierarchy

- This requires implementation of advanced intelligent computations and sophisticated powerful embedded computing technology:

- directly in the IoT edge devices related to the complex sensors and actuators, or

- just above the edge nodes, where the information from different sensors can be combined and based on the combined information the control decisions can be taken and subsequently actuated

- Sophisticated and powerful edge/dew computing has to be used requiring advanced intelligence, processing power and communication capabilities to be pushed towards the edge-nodes of IoT, where the data originates and information is used (i.e. to sensors, controllers and actuators)

- A very good example of the edge/dew computing necessity is the **local** vehicle-to-vehicle and -infrastructure communication and collaboration necessary for autonomous driving

- In consequence, the IoT for advanced (mobile) CPS will be substantially different than Internet for other traditional targets

23

### Challenges: application parallelism and heterogeneity

- The modern complex applications that require ultra-high performance and/or ultra-low energy consumption:

- are from their very nature heterogeneous

- include numerous different algorithms involving various kinds of massive parallelism: data parallelism, and task-level, instruction-level and operation-level functional parallelism

- To adequately serve these applications:

- heterogeneous computation platforms have to be exploited

- processing engines with parallel multi-processor macro-architectures and parallel processor micro-architectures have to be constructed

- different parts of complex applications involving different kinds of parallelism have to be implemented with corresponding different application-part specific parallel hardware

- multiple different or identical processors, each operating on a (partly) different data sub-set, have to work concurrently to realize the ultra-high throughput and ultra-low energy consumption

### **Challenges**: application complexity, parallelism and heterogeneity

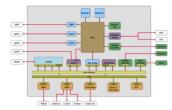

To implement the highly-demanding complex heterogeneous CPS applications complex heterogeneous MPSoCs are needed

Intel Atom Z3770\*

Nvidia Tegra 2+

<sup>\*</sup>Source: http://tweakers.net/reviews/3162/2/intels-atom-bay-trail-de-eerstenieuwe-atom-in-vijf-jaar-zes-verschillende-bay-trails.html

<sup>+</sup>Source: http://www.anandtech.com/show/4144/lg-optimus-2x-nvidia-tegra-2-reviewthe-first-dual-core-smartphone/3

### **Challenges**: application complexity, parallelism and heterogeneity

NVIDIA's advanced massively parallel heterogeneous MPSoC for ADAS and similar mobile CPS applications

### The status of computing technology for advanced CPS

- Many advanced processors and heterogeneous parallel MPSoC architectures have been proposed in the recent years

- Many of them are useful for various advanced (mobile) CPS applications

- What is the problem?

- The design methods and automated tools for:

- mapping of complex heterogeneous parallel applications to such hardware platforms

- customization of such platforms and coherent HW/SW architecture co-development

- parallel programming and code parallelization and compilation for such platforms

- development and management of autonomous evolvable distributed systems and systems-of-systems collaborating through IoT

- management of competing CPS applications, computing resources, services and workloads in the IoT hierarchy

- modeling, analysis, development, verification, validation and certification of CPS involving combined diverse cyber and physical components or sub-systems

- holistic development and multi-objective optimization of complex heterogeneous CPS

- ensuring reliability, security and safety of critical CPS

## **Challenges**: criticality of applications

- □ Cyber-physical systems influence our life to a higher and higher degree

- ☐ Therefore, the society expectations regarding them grow rapidly

- Due to CPS common usage in various kinds of technical, social and biological applications, and their growing influence, we and the life on the Earth more and more depend and rely on these systems:

- their quality is becoming more and more critical

- many applications considered previously as non-critical are becoming critical

- Due to the rapidly growing share of the highly demanding embedded and CPS applications, higher demands are becoming much more common

- Due to the multiple reasons just discussed, and specifically, due to the rapidly growing system and silicon complexity and diversity, it will be more and more difficult to guarantee the systems' quality

- □ This is a **new difficult situation** that cannot be adequately addressed without an **adequate design methodology** and **electronic design automation**

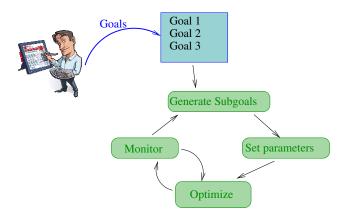

### Quality-driven Model-based Design

- When considering a **system and design methodology adaptation** to the situation in the field of modern CPS, we have first to ask: *what general system approach and design approach seem to be adequate to solve the listed problems and overcome the challenges*?

- Predicting the current situation, more than 20 years ago I proposed such system paradigm and design paradigm, i.e. the paradigms of:

- life-inspired systems and quality-driven design, and

- the methodology of quality-driven model-based system design based on them

- From that time my research team and our industrial and academic collaborators were researching the application of this methodology to the design and design automation of embedded processors, MPSoCs and CPS, and this research confirmed the adequacy of the quality-driven design methodology

- For "Outstanding Achievements and Contributions to Quality of Electronic Design" I was awarded the Honorary Fellow Award by the International Society for Quality Electronic Design (San Jose, CA, USA, 2008)

- □ What is the quality-driven design? of CPS&IoT2019 page 29

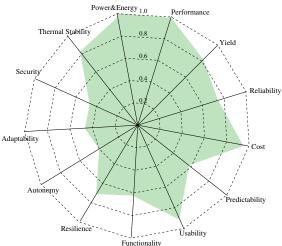

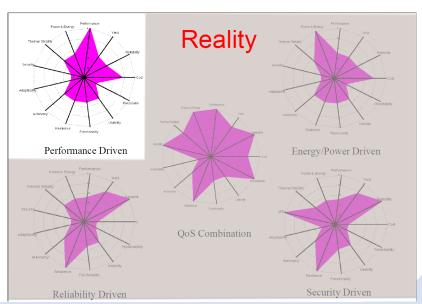

### Quality-driven design approach

- □ System design is a definition of the required quality, i.e. a satisfactory answer to the following two questions:

- What new (or modified) quality is required?

and

- > How can it be achieved?

- Intuitively we feel that quality is here used in the sense of the totality of the (important) features the system has

- So, system design should define:

- What is the required totality of the (important) system features?

and

- How to realize a system that has these all features?

- In other words:

- What process must be realized in a certain system and what structural and parametric features must have the system?

- How can we build a system that will be able to realize this process and will have the required structural and parametric features?

30

### Quality

- □ Actually, what is quality?

- □ The most used and cited definitions of quality:

- fitness for use (*Juran*)

- conformance to requirements (*Crosby*)

- quality is meeting the customers' expectations at a price they can afford (*Deming*)

- the loss of quality is the loss a product causes to society after being shipped, other than any losses caused by its intrinsic functions (*Taguchi*)

- the totality of features and characteristics of a product or service that bear on its ability to satisfy given needs (American Society for Quality Control)

- the totality of features and characteristics of a product or service that bear on its ability to satisfy stated or implied needs (ISO8402: Quality Vocabulary Part 1, International terms, 1987)

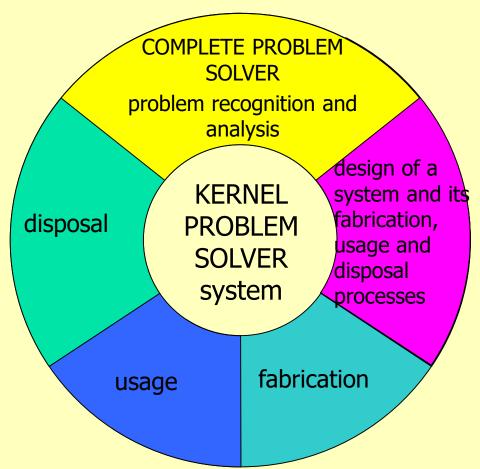

### **Problems with the existing definitions of quality**

they focus exclusively on a product being designed, while the original problem is solved by designing, fabrication, usage and disposing of the system

Quality cannot be limited to the system itself, but it must account for the complete problem solution, related to complete system life-cycle

Proceedings of CPS&LoT2019 page 32

32

#### **Problems with the existing definitions of quality**

- none of these definitions is precise enough to enable the systematic consideration, measurement and comparison of quality

- the assumption of perfectly known and inviolable customer's requirements is not acceptable, because the customer may specify the requirements poorly and such requirements may result in system which will create danger, damage environment or squander scarce resources

- engineered systems solve certain real-life problems, serve certain purposes they are purposive systems

- quality of a purposive system can only be defined in relation to its purpose

#### New quality definition proposed by me 20 years ago

# Quality of a purposive systemic solution is its total effectiveness and efficiency in solving of the real-life problem that defines the solution's purpose

- ☐ Effectiveness = the degree to which a solution attains its goals

- Efficiency = the degree to which a solution uses resources in order to realize its aims

- ☐ Effectiveness and efficiency of a systemic solution together decide its grade of excellence their aggregation expresses quality

- Effectiveness and efficiency can be expressed in terms of measurable parameters, and in this way, quality can be modeled and measured

- In particular, the quality can be modeled in the form of multi-objective decision models involving measurable design parameters

- The multi-objective decision models and design parameter estimators enable application of the multi-objective decision methods for construction, improvement and selection of the most promising solutions

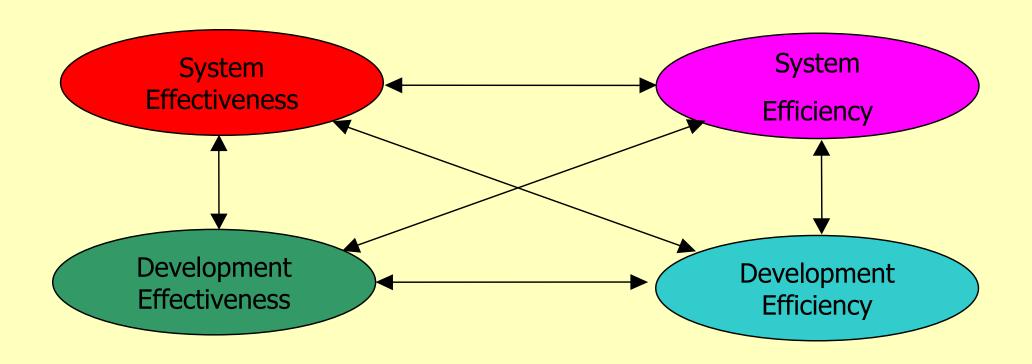

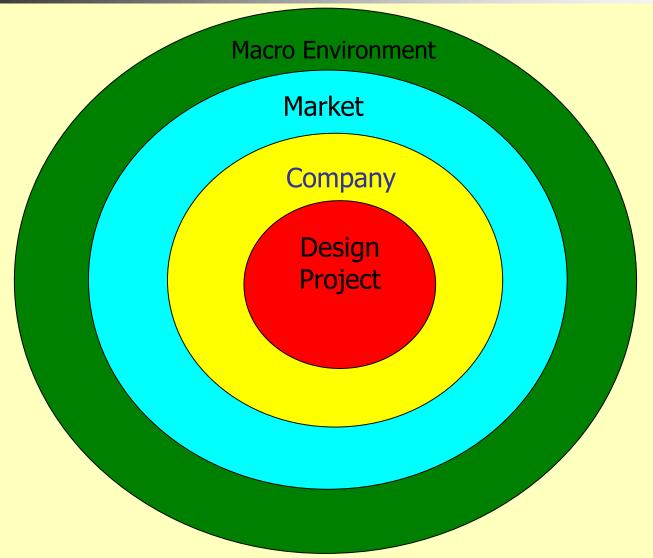

Interactions and trade-offs between various parts and aspects of the total systemic solution

Interactions of a design project with its context

- Design does not concern the reality as it is, but as it will possibly be realized

- Quality recognition and formulation, i.e. recognition of the problem, as well as of the nature of its solution are subjective to a high degree

- The contemporary system design problems are complex, multiaspectual, dynamic, and ill-structured:

- there is no definitive formulation of the problem,

- any problem formulation may be inconsistent,

- formulations of the problem are solution dependent,

- proposing and considering solutions is a means for understanding the problem, and

- there is no definitive solution to the problem

- ☐ The complex design problems are ill-defined

- It is very difficult to find precise relations between various aspects of the system effectiveness and between the different forms of energy and matter used to attain the system's aim, and even more difficult to express them as one uniform measure

- ☐ There are trade-offs as well between effectiveness and efficiency as among different their aspects

- ☐ The required quality or its perception can change in time

quality cannot be well defined, but it can and should be modelled

#### Quality-driven Design - Design models

- □ Well-structured models of the required/delivered quality can serve to:

- conceptualize, denote, analyse and communicate the customer's and designer's ideas

- > show that the requirements and designs are meaningful and correct

- guide the design process

- enable the explicit and well-organized design decision making

- enable design automation

- > etc.

#### Quality-driven Design: Design problem-solving using models

- Since the system design problems are:

- complex;

- multi-aspect;

- ill-defined,

to solve them, all human concepts for dealing with complexity, diversity and ill-structure have to be applied:

- abstraction;

- separation of concerns;

- decomposition and composition;

- generalization and specialization;

- modelling;

- simulation;

- prototyping;

- ....

- □ A design problem has to be converted into a system of simpler subproblems

- ☐ The solution to the original problem can then be achieved by solving the subproblems and composing the sub-problem solutions into an aggregate solution

#### Quality-driven Design: Design problem-solving using models

- The problem decomposition and design modelling are to some degree subjective

- The design decision processes are also to some degree subjective, as they are influenced by the designers' value systems, feelings, believes, intuition etc.

- ☐ The design problem solving activity is performed under uncertainty, inaccuracy, imprecision and risk conditions, and in a dynamic environment

**U**

System design has to be an evolutionary process in which analysis and modelling of problems; proposing their solutions; analysis, testing and validation of the proposals; learning and adapting are very important

#### Main concepts of the quality-driven design

- ☐ Designing *top-quality systems is the aim* of a design process

- Quality is modelled and measured (in particular, in the form of the multiobjective decision models) to enable invention and selection of the best alternatives and quality improvement

- □ Quality models are considered to be heuristics for setting and controlling the course of design

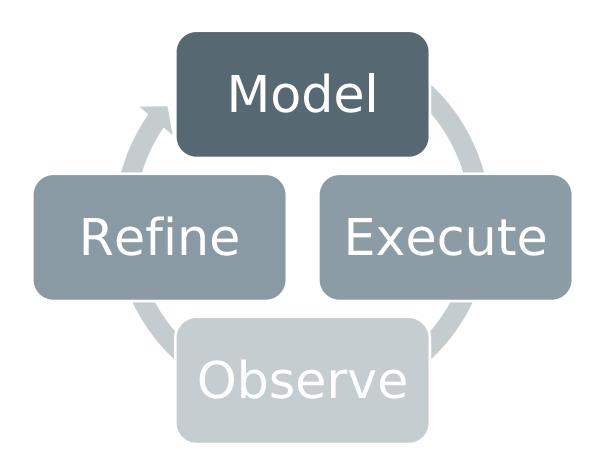

- ☐ The design process is evolutionary and it basically consists of:

- constructing the tentative quality models,

- using them for constructing, improving and selecting of the tentative solutions,

- analysing and estimating them directly and through analysis of the resulting solutions,

- improving the models, and using them again to get improved solutions, etc.

#### Main concepts of the quality driven design

- ☐ In the design process, a balance is sought for between the effectiveness and efficiency, and among all their important aspects; in particular between:

- the multiplicity of the life-cycle aspects considered in parallel and the amount of iteration

- between design reuse and innovation

- between art and science in the design

- between the designers subjective inventive thinking and objectivity increasing constraints and regulations

- between the human designer's involvement and automation.

- ☐ Criterium for this balance is *total effectiveness and efficiency of a design process*

#### Quality-driven Design: Limiting the design subjectivity

□ One of the main aims of using the well-defined models in design is:

Limiting the scope of subjective design decision making and enlarging the scope of reasoning-based decision making with clear and well-defined rational procedures which can be computerized

- □ Too much subjectivity in design may result in solutions that either do not solve the actual real-life problem or do not do it in a satisfactory manner

- Limiting the design subjectivity in an appropriate manner, when enabling the creativity exploitation at the same time, is necessary to arrive at the high-quality designs

#### Quality-driven Design: Limiting the design subjectivity

- ☐ The main means for limiting the design subjectivity is the design space exploration (DSE) with usage of the well-structured quality models

- **Exploration** of the abstract models of the required quality and more concrete solutions obtained with these models:

- > gives much and more objective information on the design problem, its possible and preferred solutions, and various models used in this process

- > enhances exploitation of the designer's imagination, creativity, knowledge and experience

- Other important means for limiting the design subjectivity include:

- appropriately organised team-work

- benchmarking and comparison with both own previous designs and designs of competition

- design analysis and validation

- > design reuse

- government and branch regulations and standards

#### Quality-driven Design - Design requirements

- ☐ The **general model of the required system's quality** is represented by the **system (design) requirements**

- Not "the conformance to requirements" (P.B. Crosby), but the solution of the actual real-life design problem with a satisfactorily high total effectiveness and efficiency is important

- Requirements can only be treated as a non-perfect and tentative model of the required quality

- ☐ The requirements and the solutions obtained with their use should be confronted with the actual up-to-date needs many times during the design process, and replaced or modified, if necessary

- Requirements and any other quality models are not sacred and inviolable, but they are subject to design and change

#### Quality-driven Design - Design requirements

- Design requirements represent a model of the required quality that models the design problem at a hand through the imposition of a number of constraints and objectives in relation to the acceptable or preferred problem solutions

- ☐ It is thus an *abstract model of a solution to the problem*.

- Since such a model limits the space of acceptable or preferred solutions to a certain degree only, it *models many solutions concurrently*.

- Each of the **solutions fulfils all the hard constraints** of the model, but different solutions can **satisfy its objectives to various degrees**.

- ☐ It is possible to distinguish **three sorts of requirements:**

- > functional,

- > structural, and

- parametric

#### Quality-driven Design - Design requirements

□ All the three sorts of requirements impose limits on the structure of a required solution, but they do it in different ways

- ☐ The **structural requirements** define the acceptable or preferred solution structures directly, by limiting them to a certain class or imposing a preference relation on them

- ☐ The *parametric requirements* define the structures indirectly, by requiring that the structure has such physical, economic or other properties (described by values of some parameters) as fulfil given constraints and satisfy stated objectives

- ☐ The *functional requirements* also define the structures indirectly, by requiring the structure to expose a certain externally observable behaviour that realizes the required behaviour

#### Quality-driven design space exploration (DSE)

- □ **System design is an evolutionary quality engineering process** in which the concepts of analysing and modelling problems, proposing their solutions, analysing and testing the proposals, learning and adapting are very important

- It starts with an abstract, and possibly incomplete, imprecise, and contradictory, initial quality model (initial requirements)

- It tries to transform the initial model into a concrete, precise, complete, coherent and directly implementable final model

- ☐ The initial abstract model mostly involves some behavioural and parametric characteristics and to a lesser extend the structure definition

- ☐ The **final model** defines the **system's structure explicitly**

- This structure supports the system's required behaviour and satisfies the parametric requirements

#### Quality-driven DSE

- □ During the design process the structural information is gradually added by the designers and synthesis tools to the created (partial) solutions.

- ☐ This evolutionary quality engineering processes applies the *problem-solving* framework of heuristic search and decomposes the total design problem into several issues.

- ☐ In this framework, the process of design problem solving can be represented by a *design search tree*:

- the tree's nodes correspond to various design issues (sub-problems)

- the tree's branches correspond to various design options (alternative solutions)

- for each issue, many various alternative solutions are typically possible.

- ☐ A **design decision** is a choice of a particular option, or the option chosen

- Each option chosen may recursively raise new issues, expanding the design search tree downwards until a final design will be obtained

50

#### Quality-driven design space exploration

- For each issue, many various alternative solutions are typically possible.

- □ For each issue, we can construct some issue's quality models, composed of some selected and abstracted functional, structural and parametric requirements extracted in an appropriate manner from the total quality model of the considered system.

- In particular, the issue's decision model can be constructed that is a base for decision making in the scope of a certain issue

- A decision model is a *partial* (reduced to only certain concerns) and *abstract* (reduced to the necessary and/or possible precision level) **model** of the required quality, *expressed in the decision-theoretical terms*.

- Decision models and design parameter estimators enable application of the multi-objective decision methods for construction, improvement and selection of the most promising solutions.

#### Quality-driven Design - Decision models

- □ The decision model of a given issue must account for all system characteristics substantially relevant to the issue

- ☐ It must specify preferences of values for all the characteristics, expressed by hard constraints, objectives, and trade-off information

- For each single characteristic, the preferences of its values can be characterized by specifying a utility (effectiveness or efficiency) function  $u_i(x_i)$  for the characteristic  $x_i$

- Each utility function  $u_i(x_i)$  describes the level of satisfaction from a particular value of the characteristic  $x_i$

- Due to the multi-aspect nature of systems and possible trade-offs, the relative importance of different characteristics or the reference points in the utility space have to be specified

#### Quality-driven Design - Decision models

- This can be done in different ways dependent on the problem characteristics, for example by:

- establishing an order for the objectives,

- constructing a multi-objective utility function,

- defining ranking information,

- establishing local preferences for small changes in values of the objectives, or

- defining some reference (aspiration) points in the utility or parameter space

- With such models the total system quality Q can be modelled as a function of utility levels of all the important system characteristics influencing the systems effectiveness or efficiency

- Such design decision models make it possible to apply the multiobjective decision methods for invention and selection of solutions that are "totally optimal"

## Modeling quality Q as a (vector) function of utility levels of the system characteristics

$$Q(y) = Q(x_1(y), x_2(y), ..., x_n(y)) = F(v_1(x_1), v_2(x_2), ..., v_n(x_n))$$

Attributes

a b c d e f

Hierarchy of Atributes

Physical Measures

$$x_1 \quad x_2 \quad x_3$$

$$x_4$$

Utility Functions

$$v(x_1)$$

$$x_1 \quad v(x_2)$$

$$x_2 \quad v(x_3)$$

$$x_3$$

Tradeoffs:

- Relative Importance Among Attributes

or

54

- Reference Points in Utility Space (or Parameter Space)

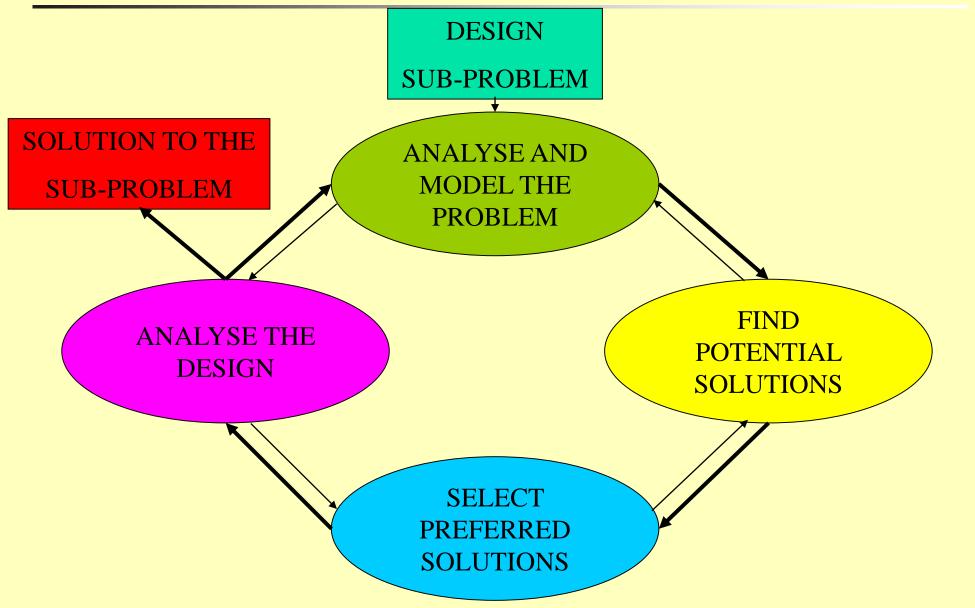

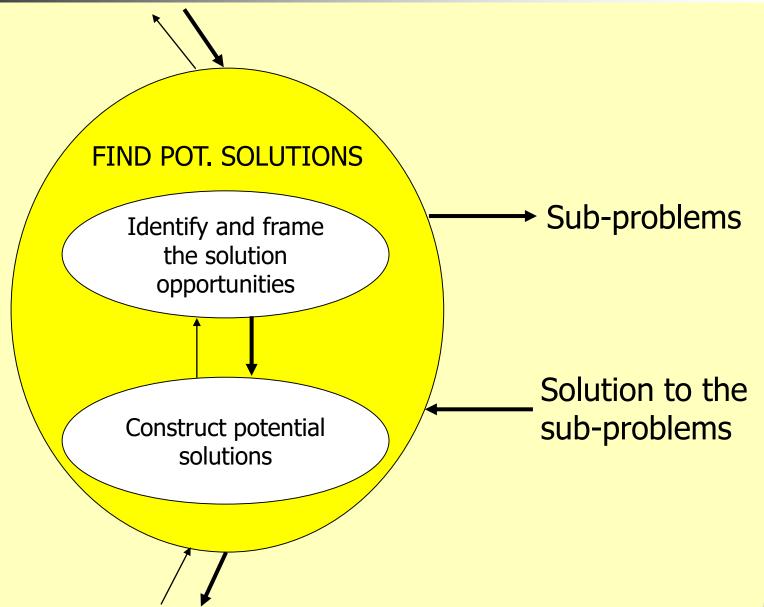

#### Generic model of the quality-driven design space exploration

#### Quality-driven design space exploration

- The quality-driven design space exploration basically consists of the alternating phases of:

- exploration of the space of abstract models of the required quality

and

- exploration of the space of the more concrete issue's solutions obtained with the chosen quality models

- ☐ In this way, both:

- "let's make better things"

and

- "let's make things better"

will be brought into effect.

#### Generic model of the quality-driven design space exploration

#### Quality-driven design space exploration

- In result of the design space exploration, the considered system is defined as an appropriate decomposition into a network of sub-systems

- Each sub-system solves a certain sub-problem

- All sub-systems cooperating together solve the system design problem by exposing the external aggregate behaviour and characteristics which match the required behaviour and characteristics

- □ The design process breaks down a complex system defined in abstract and non-precise terms into a structure of cooperating sub-systems defined in more concrete and precise terms, which are in turn further broken down to the simpler sub-systems that can be directly implemented with the elements and sub-systems at the designer's disposal

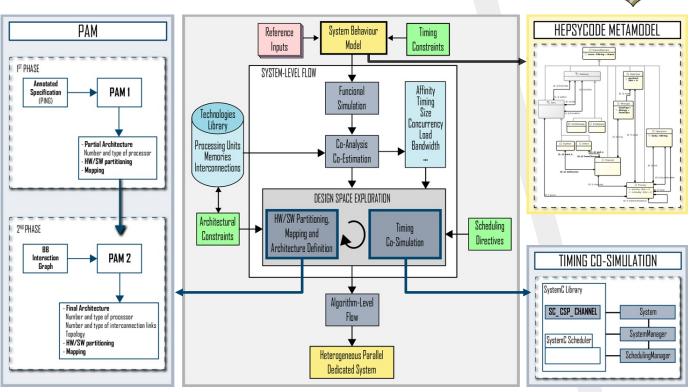

## **Example**: Quality-driven model-based automated design of multi-ASIP MPSoCs (ARTEMIS ASAM project Grant No. 100265)

- □ To develop the required complex multi-ASIP MPSoCs, a sophisticated design space exploration is necessary in which only the most promising ASIP and MPSoC architectures will be efficiently constructed, and the best of these architectures will be selected for further analysis, refinement and actual implementation

- The ASAM multi-ASIP MPSoC design-space exploration implements the qualitydriven model-based system design methodology

- According to this methodology, to bring the quality-driven design into effect, quality has to be modeled, measured, and compared

- □ The **quality** of the multi-ASIP MPSoC required is modeled in the form of the:

- demanded system behavior (application c-code)

- structural constraints: generic ASIP and MPSoC architecture templates and their pre-characterized generic parts included in the IP library, and

- parametric constraints and objectives to be satisfied by the MPSoC design

- Based on the analysis of the so modeled required quality, the generic architecture templates are adequately instantiated and used in **design space exploration** that **constructs** one or several most promising MPSoC designs supporting the required behavior and satisfying the demanded constraints and objectives

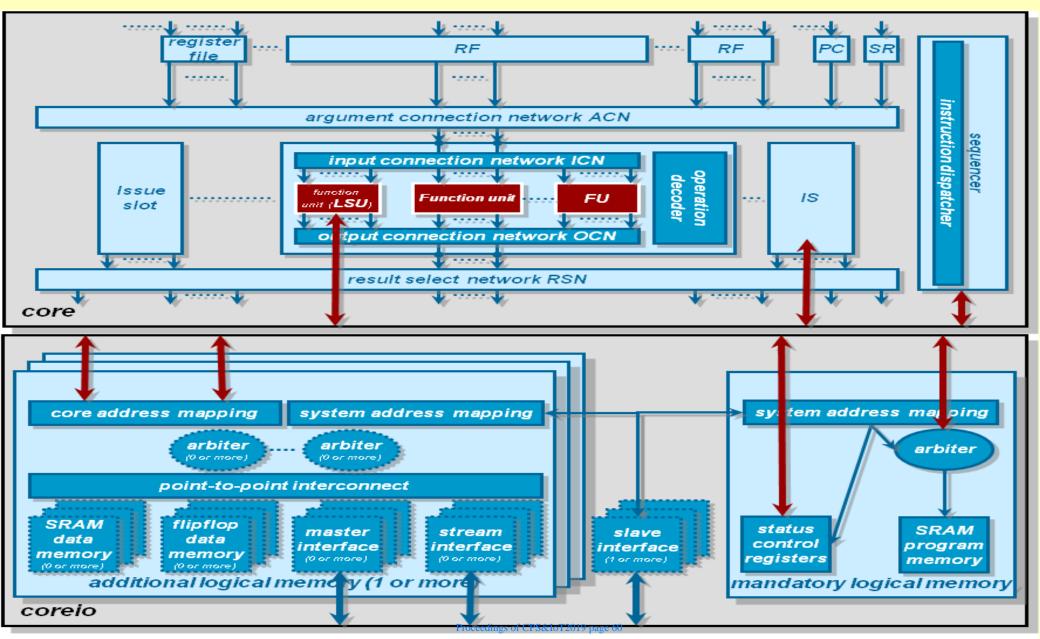

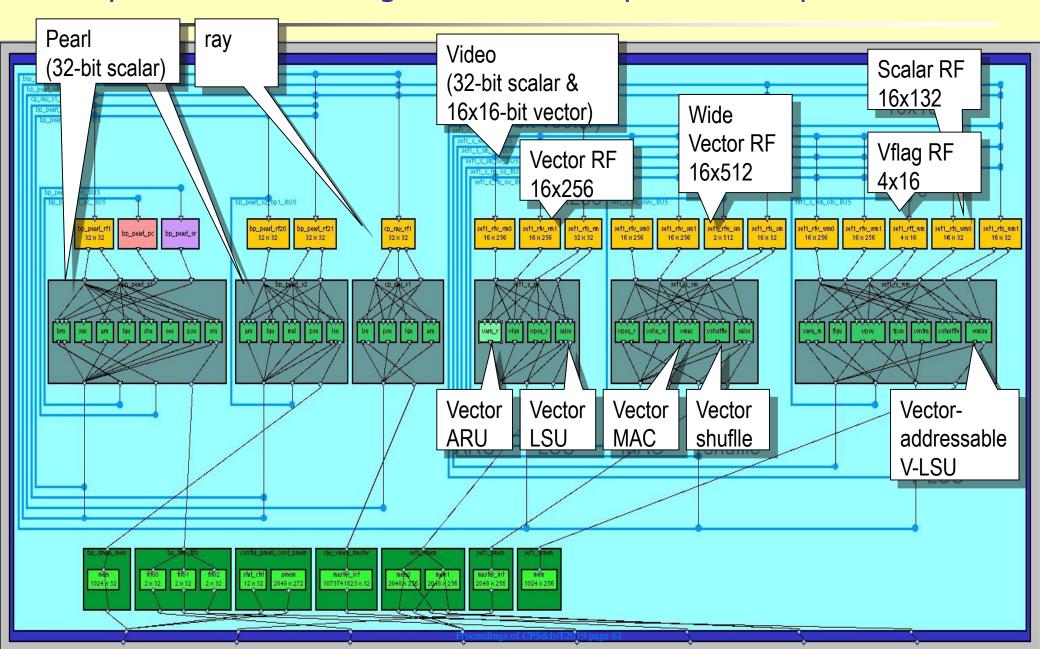

## Example of Generic WLIW ASIP Architecture Template (Intel Benelux, used in ASAM project)

#### Example instance of the generic ASIP template: video processor

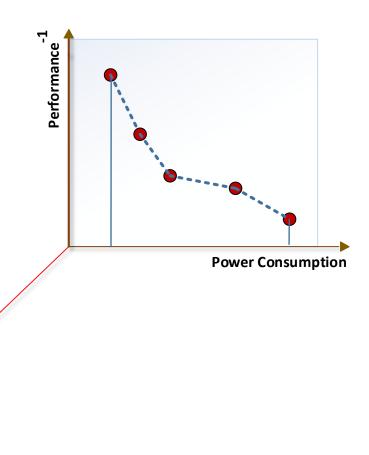

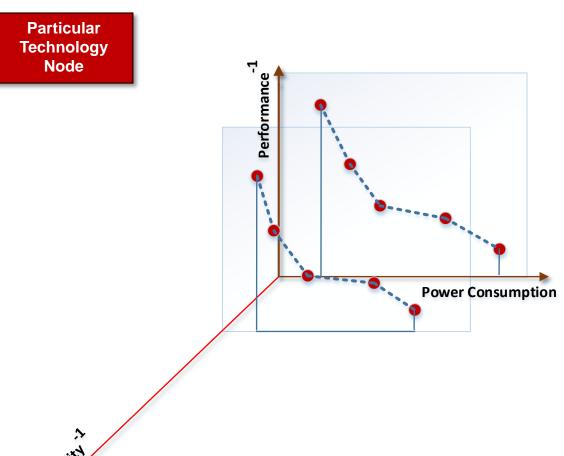

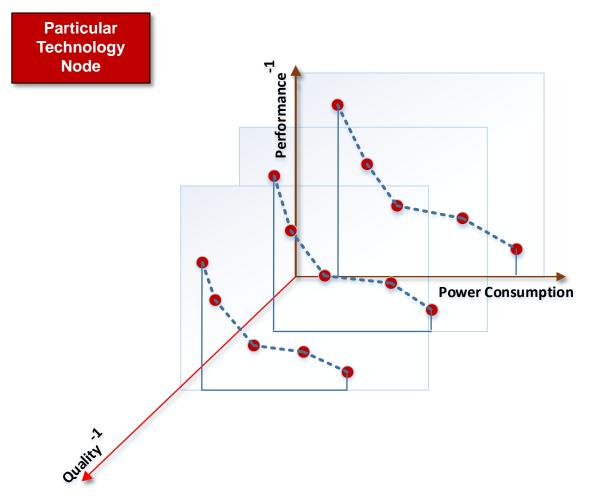

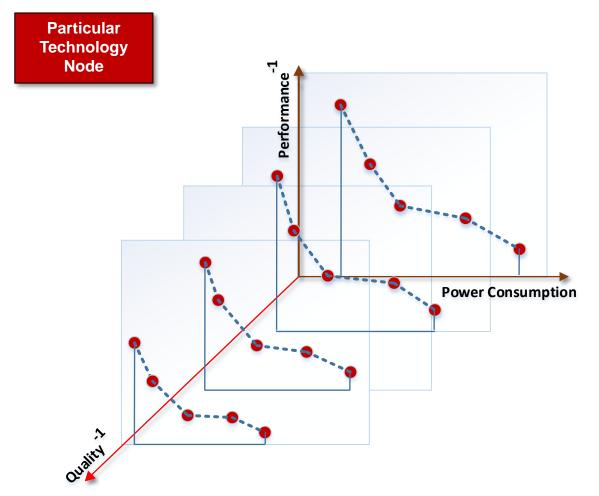

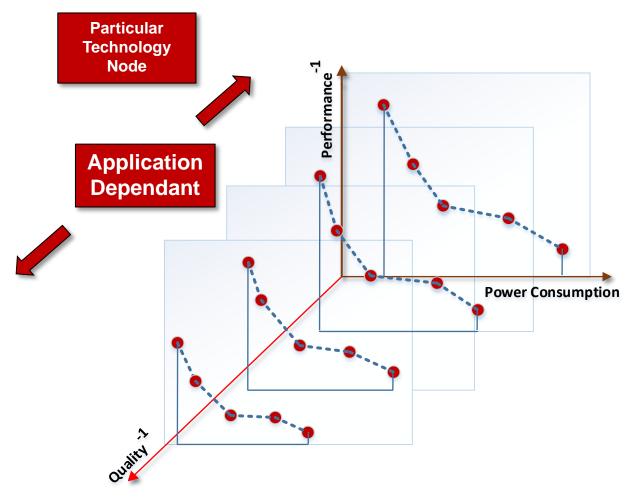

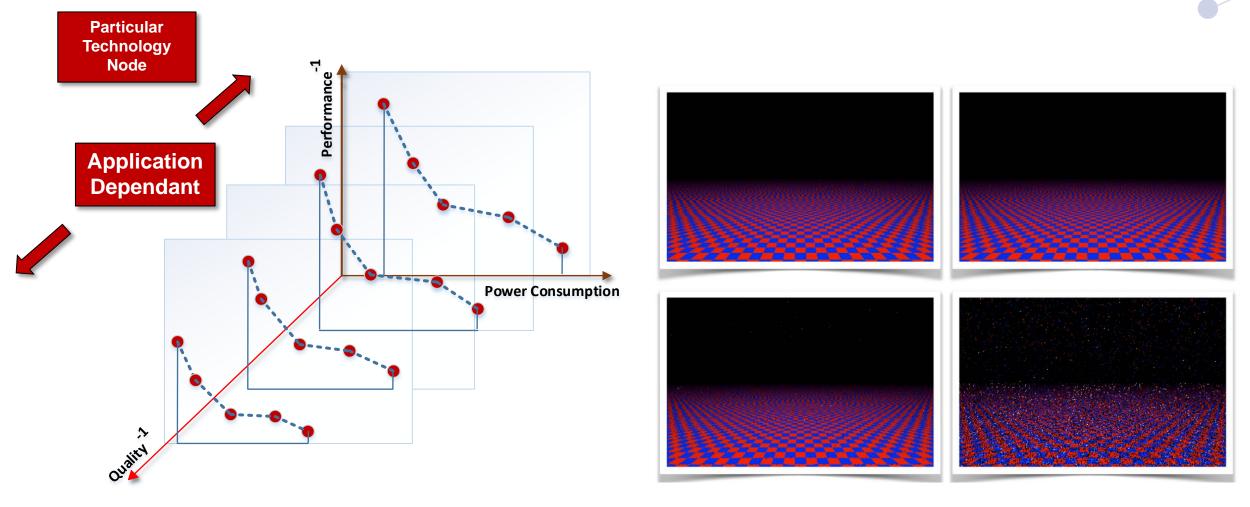

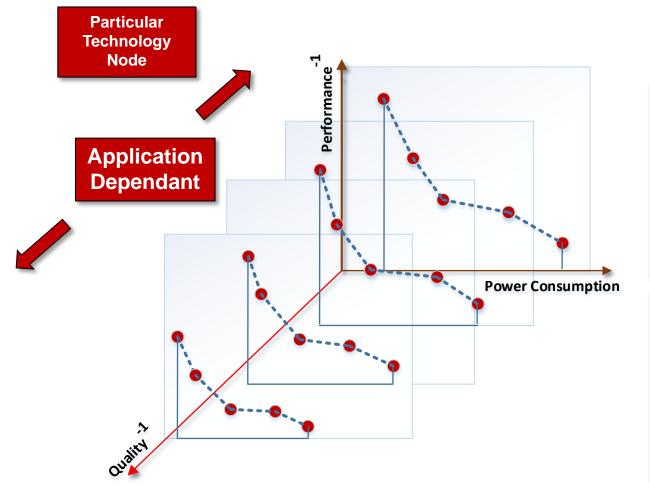

# Quality-driven model-based automated design of multi-ASIP MPSoCs: Quality-driven DSE

- Based on the analysis of the so modeled required quality, the generic architecture template is adequately instantiated and used in **design space exploration** that aims at:

- analysis of various architectural choices regarding:

- processor micro-architectures and multi-processor macro-architecture

- parallel memories architectures

- parallel communication architectures

- macro-/micro-architecture tradeoffs

- processor, memory and communication tradeoffs,

and based on this analysis,

construction of one or several most promising (sub-)system architectures supporting the required behavior and satisfying the demanded constraints and objectives.

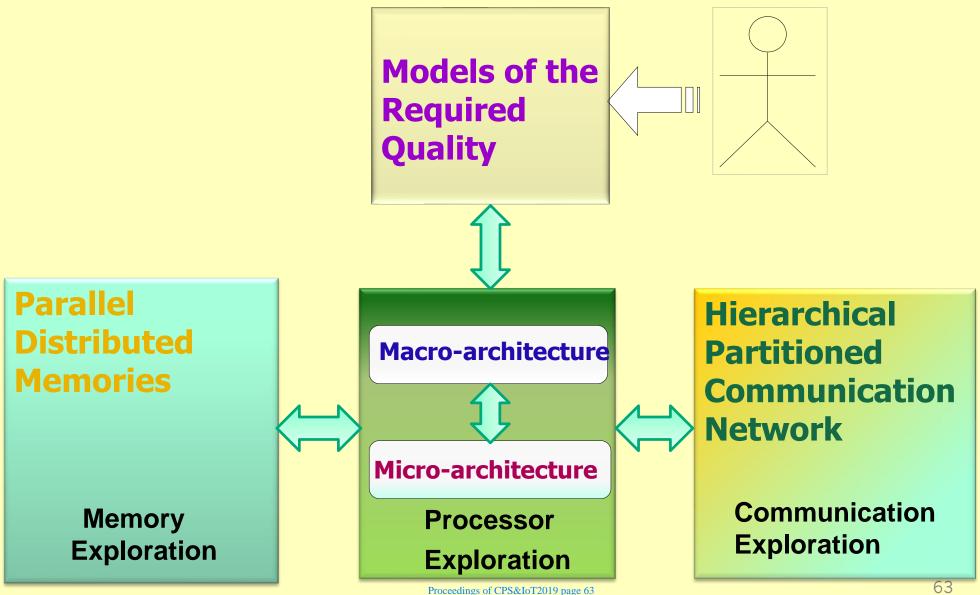

#### Quality-driven DSE: General Organization

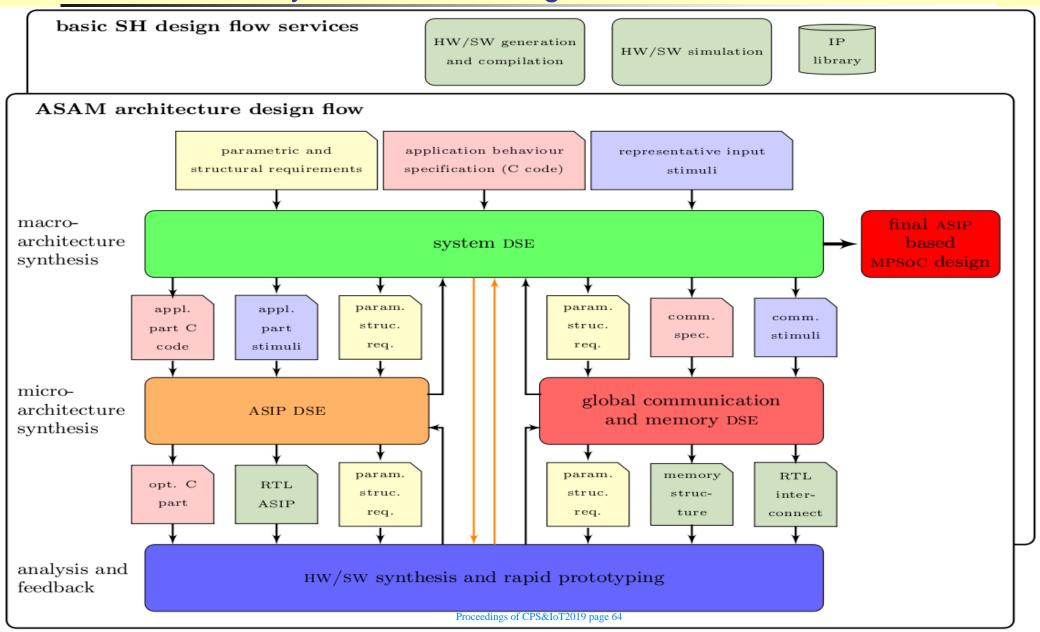

## **ASAM main result**: quality-driven design method, flow and tools for the automated synthesis of heterogeneous ASIP-based MPSoCs

#### Conclusion

- Many modern CPS applications are complex, heterogeneous, involve big data and massive parallelism, and demand an (ultra-)high performance and/or (ultra-)low energy consumption, while requiring a high reliability, safety and security

- Many parallel processors and heterogeneous MPSoC architectures have been proposed in the recent years, and some of them are useful for various advanced CPS applications

- The related design methods and automated tools are much less advanced

- Although much research on various aspects of CPS, and design methods and automated tools for CPS has been performed, and a reasonably solid methodological base has been created, much more work has still to be done

- In this CPS&IoT Summer School you will have a unique occasion to be informed on and to discuss the most recent European R&D developments in CPS and IoT

## **CPS-IoT summerschool**

# Embedded Processors for Cyber-Physical Systems

Henk Corporaal

www.ics.ele.tue.nl/~heco

h.corporaal@tue.nl

June 10-13, 2019

#### Lecture overview

- Some history

- Processor basics

- Memory hierarchy

- Advanced processor system design

- the advanced concepts of today you'll see tomorrow in the low end CPS

- Example system: EEG monitoring system

- Interesting CPS development processors & boards

Conclusions

Crash Course

5/23/2019 ECA H.Corporaal Proceedings of CPS&IoT2019 page 67

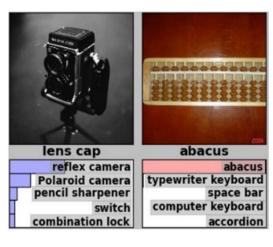

### A long history: Earliest computers

- Mechanical

- Charles Babbage: Difference Engines

- Electro-Mechanical

- Konrad Zuse's Z1, Z2, Z3

- First Electronic

- ENIAC

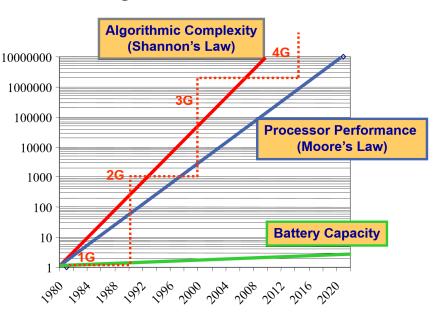

Part of Difference Engine 1, 1832

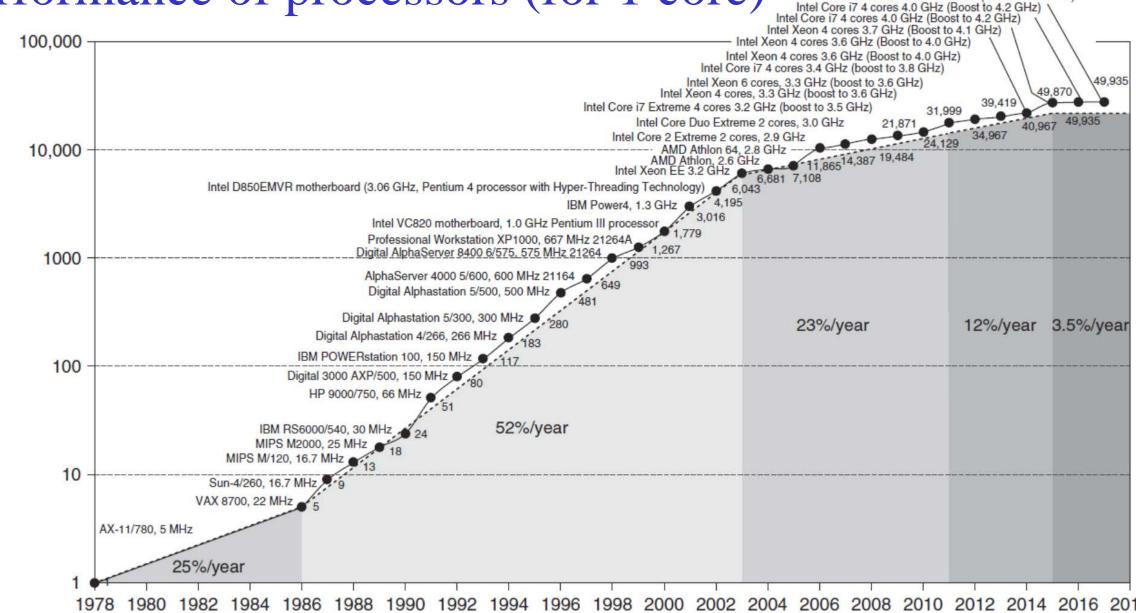

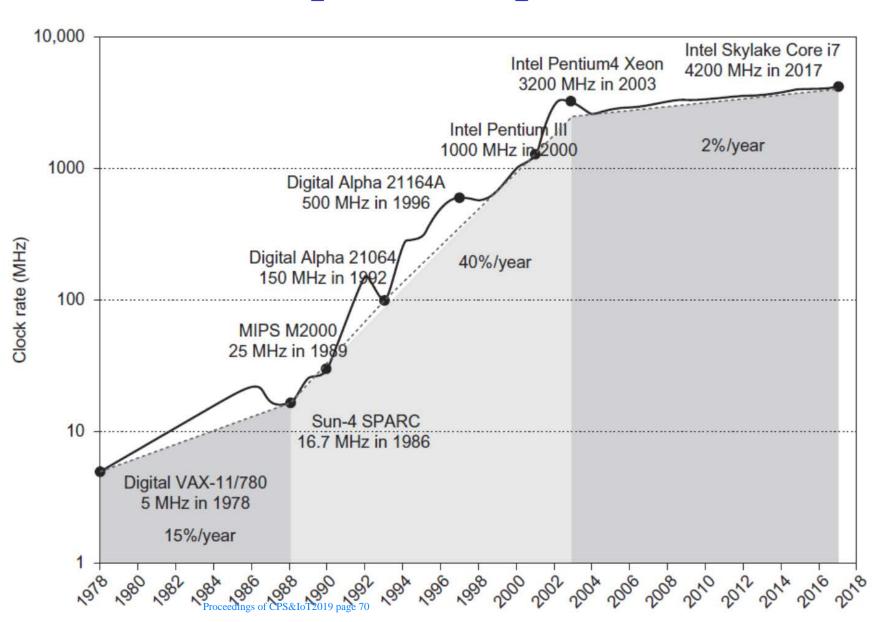

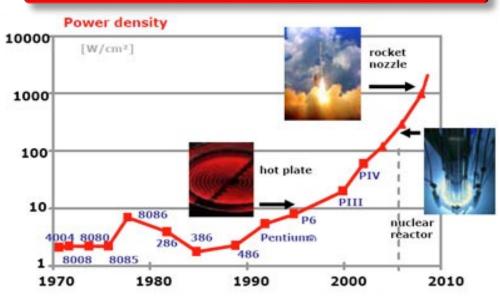

## Performance of processors (for 1 core)

ECA H.Corporaal

## Frequency and Power development of processors

- Intel 80386 consumed ~ 2 W

- 3.3 GHz Intel Core i7 consumes 130 W

- Heat must be dissipated from 1.5

x 1.5 cm chip

- This is the limit of what can be cooled by air

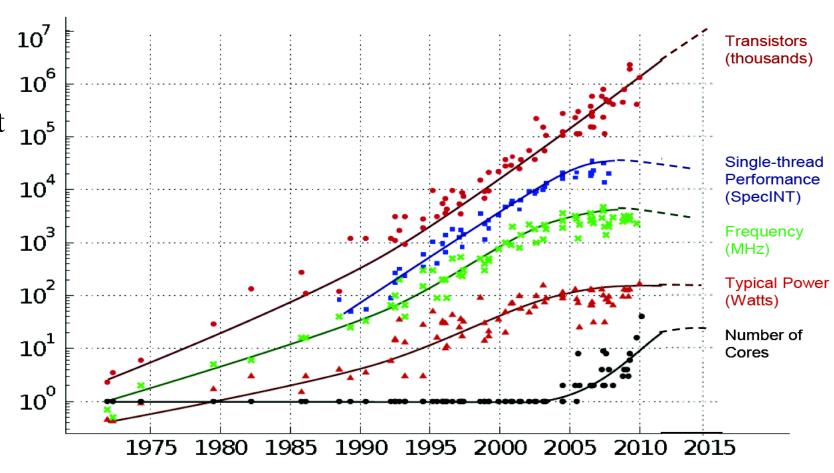

## Processor history

#### 35 YEARS OF MICROPROCESSOR TREND DATA

### Trends:

- #transistors follows Moore

- but slows down somewhat

- not clear what happens below 3-5 nm

- frequency and performance/core do not scale further

Original data collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond and C. Batten Dotted line extrapolations by C. Moore

## A small processor board: Arduino MKR GSM 1400

68x25 mm, 32 gr

- ARM Cortex M0 32-bit

- 256 KB flash

- 32 KB SRAM

- upto 48 MHz

## The other extreme: Summit, Nr 1 in the Top 500

- IBM Summit

- 122.3 petaflops on Linpack

- 4356 nodes

- per node:

- 2x 22-core Power9

- 6 NVIDIA Tesla V100 GPUs

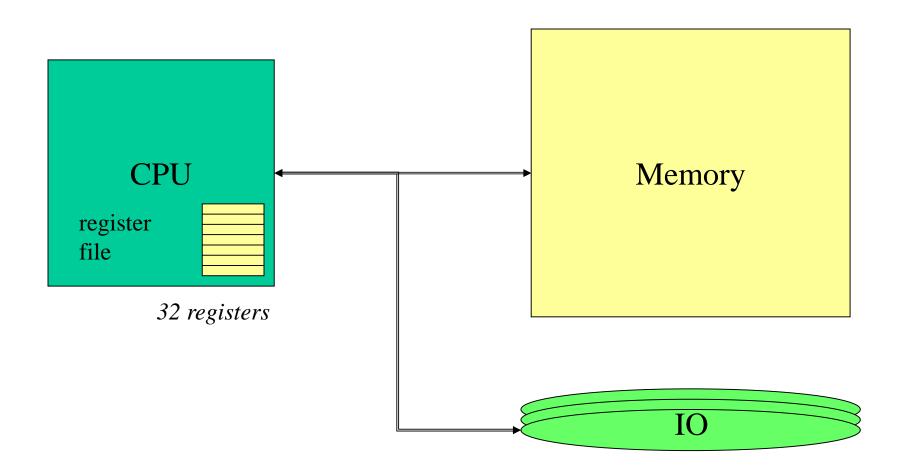

# Processor basics: structure of any computer system How does it operate?

## The Big Picture

High-level Language

Assembly Language

Machine Language

C/Java Compiler

Fortran Compiler

```

lw $to, 0($2)

lw $t1, 4($2)

sw $t1, 0($2)

sw $t0, 4($2)

```

$\Box$

MIPS Assembler

```

0000 1001 1100 0110 1010 1111 0101 1000 1010 1111 0101 1000 1010 1110 0110 1100 0110 1100 0110 1100 0110 1001 1000 0000 1001 0101 1000 0000 1001

```

## Types of Instructions of any Computer

The core ISA is easy: we need only 3 types of instructions/operations:

- Arithmetic

- Integer

- Floating Point

- Memory access

- Loads & Stores

- Control flow

- Jump

- Conditional Branch

- Call & Return

- Interrupts

Q: what's the difference between an operation and an instruction?

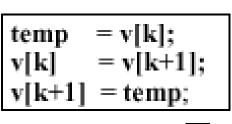

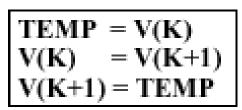

## Instructions: Load and store

• Example:

```

C code: A[8] = h + A[8];

MIPS code: lw $t0, 32($s3)

add $t0, $s2, $t0

sw $t0, 32($s3)

```

- Store word operation has no destination (register) operand

- Remember: on a RISC processor arithmetic operands are in registers, not in memory!

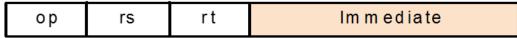

## Machine Language: Load & Store

• Example: lw \$t0, 32(\$s2)

• Introduce a new type of instruction format: I-type

**Question**: Where's the compromise?

## A typical RISC: the MIPS

• <u>Instruction</u>

### Meaning

```

add \$s1,\$s2,\$s3 \$s1 = \$s2 + \$s3

sub \$s1,\$s2,\$s3 \$s1 = \$s2 - \$s3

lw \$s1,100(\$s2) \$s1 = Memory[\$s2+100]

sw \$s1,100(\$s2) Memory[\$s2+100] = \$s1

bne \$s4,\$s5,L Next instr. is at Label if \$s4 \neq \$s5

beq \$s4,\$s5,L Next instr. is at Label if \$s4 = \$s5

j Label Next instr. is at Label

```

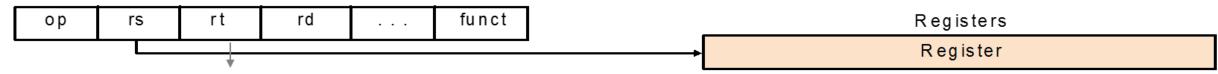

• 3 Formats:

| R | op | rs             | rt | rd             | shamt | funct |

|---|----|----------------|----|----------------|-------|-------|

| I | op | rs             | rt | 16 bit address |       |       |

| J | op | 26 bit address |    |                |       |       |

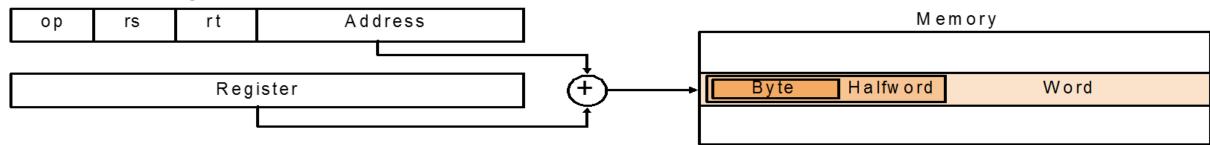

## Keep it simple: only 3 data addressing modes

#### 1. Immediate addressing

#### 2. Register addressing

#### 3. Base addressing

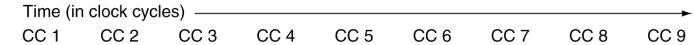

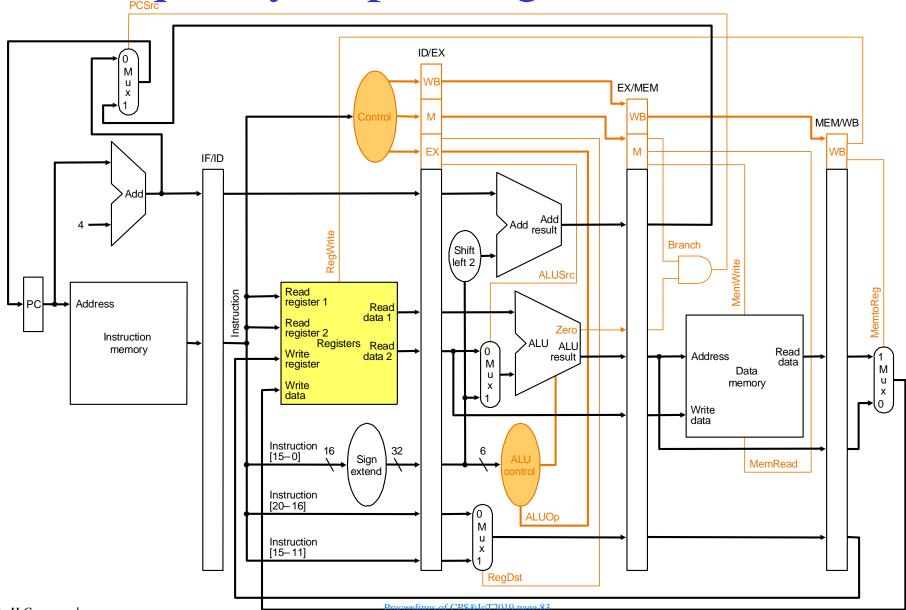

## Raise the frequency: Pipelining

5/23/2019 ECA H.Corporaal Proceedings of CPS&IoT2019 page 81

# Raise the frequency: Pipelining

5/23/2019 ECA H.Corporaal

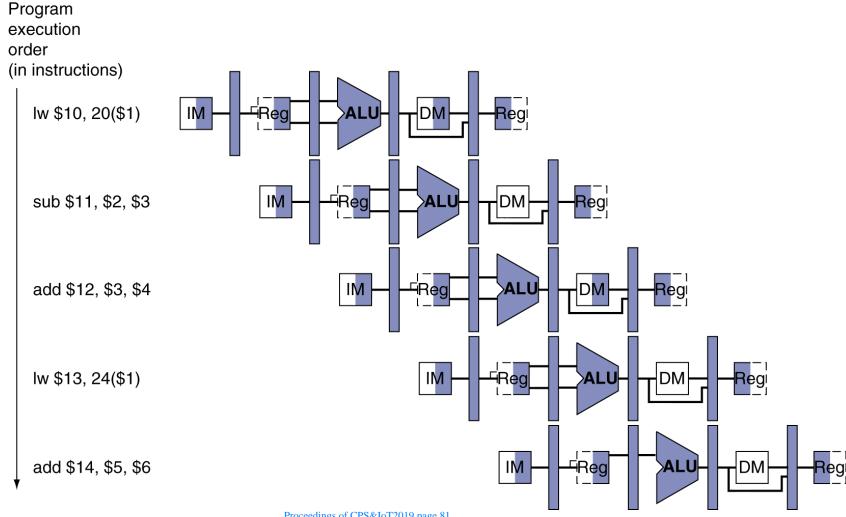

# Raise the frequency: Pipelining details, with control

5/23/2019

ECA H.Corporaal

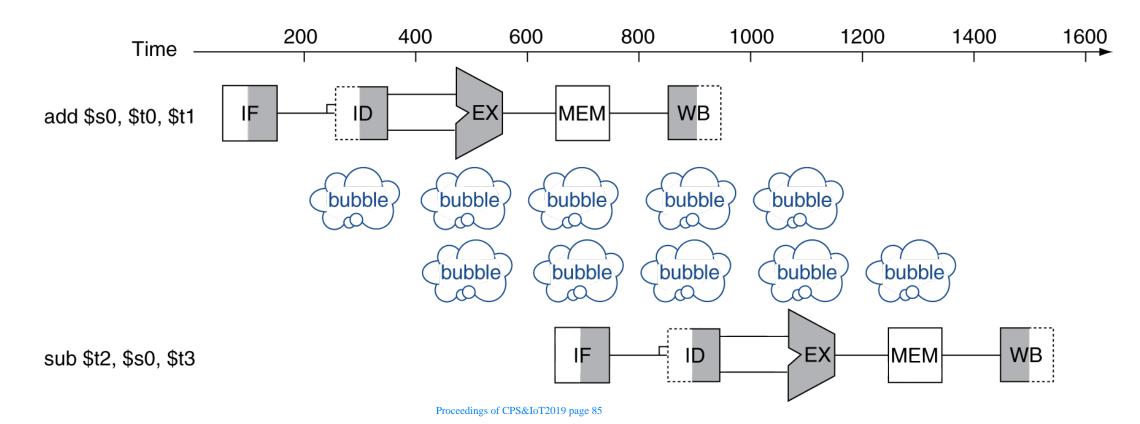

## Hazards: problems due to pipelining

Hazards: can not start next instruction in next cycle

3 types:

#### Structure hazards

A required resource is busy

#### Data hazard

Need to wait for previous instruction to complete its data read/write

#### Control hazard

Do not know (directly) what the next instruction is

## **Data Hazards**

An instruction depends on completion of data access by a previous instruction

```

add $s0, $t0, $t1

sub $t2, $s0, $t3  // RaW dependence on $s0

```

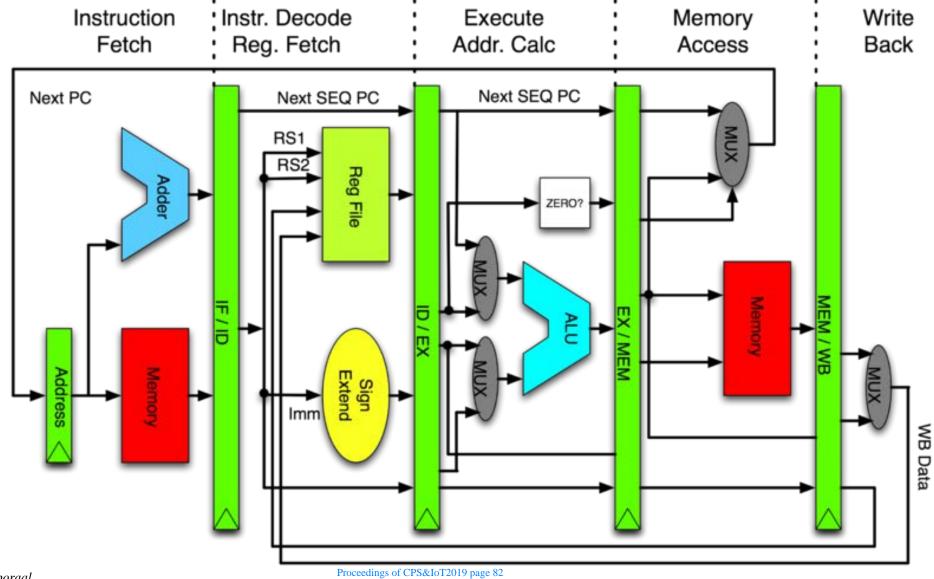

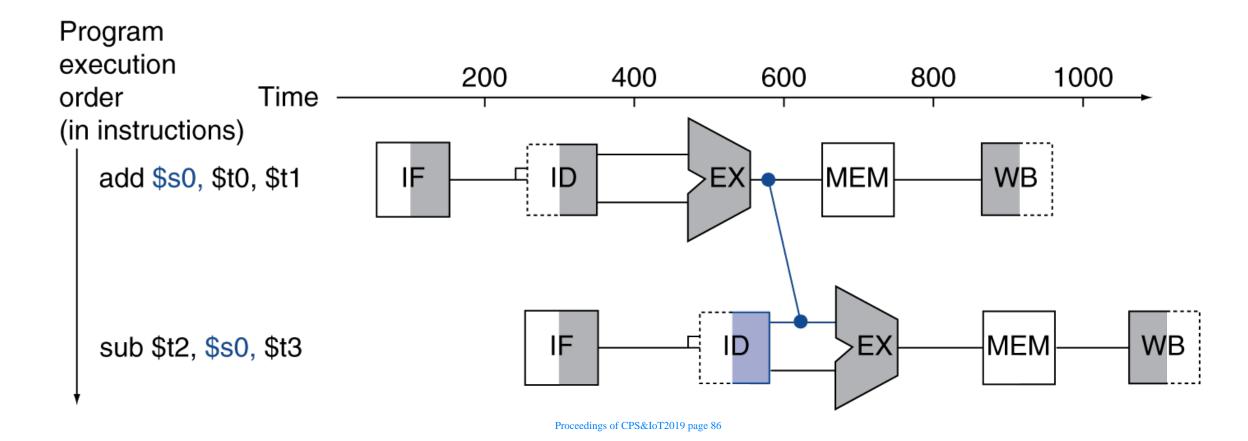

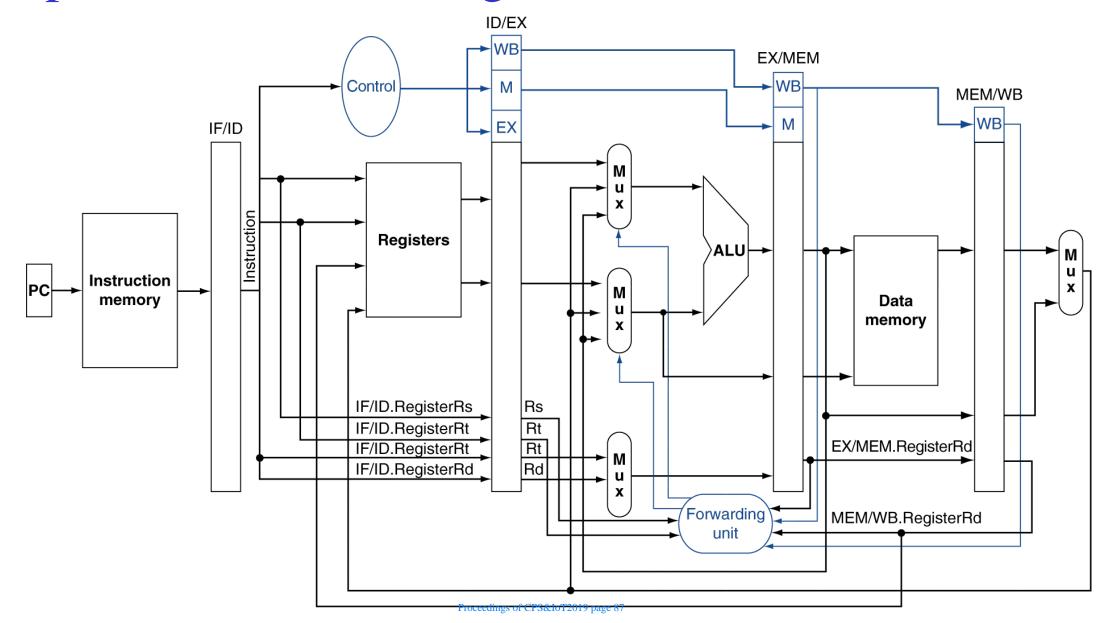

## Forwarding (aka Bypassing)

- Use result when it is computed ASAP (as soon as possible)

- Don't wait for it to be stored in a register

- Requires extra connections in the datapath

## Datapath with Forwarding

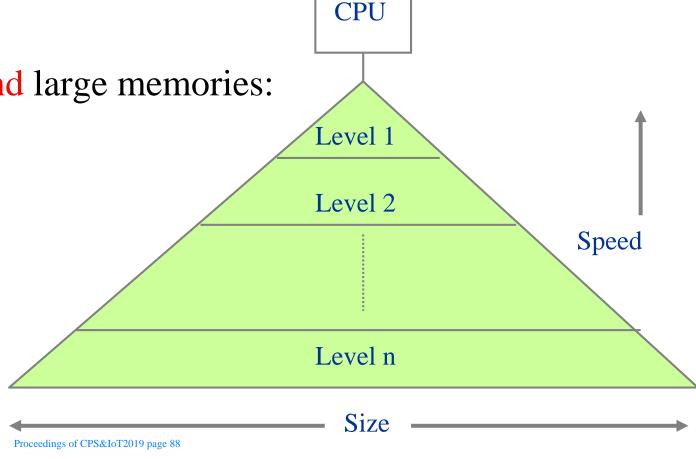

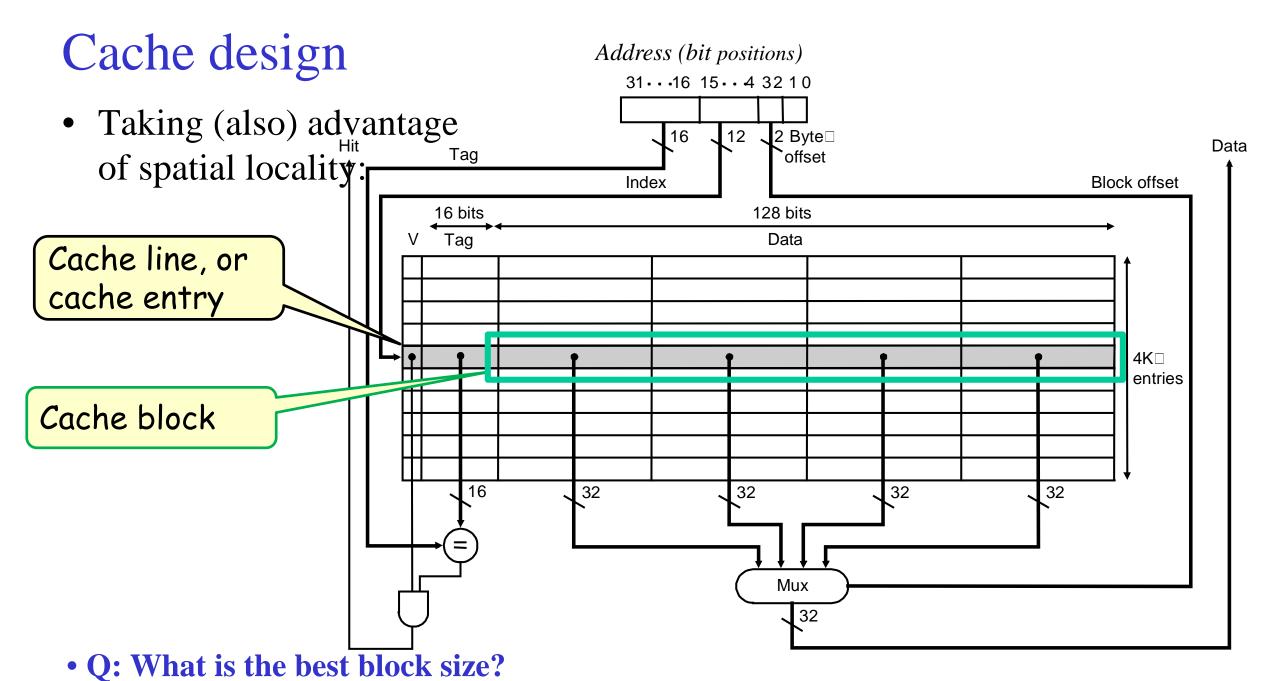

## Memory Hierarchy, why?

Users want large and fast memories!

SRAM access times are 1 - 10 ns

DRAM access times are 20 - 120 ns

Disk access times are 5 to 10 million ns, but it's bits are very cheap

• Get best of both worlds: fast and large memories:

build a memory hierarchy

• Q: why does it work, such a small level-1 memory?

Proceedings of CPS&IoT2019 page 89

## Solving collisions: 4-Way Set Associative Cache

• 256 sets, each with 4 ways Byte offset 31 30 ... 11 10 9 ... 2 1 0 (each with 1 block) 22 Tag Index V Tag ndex V Tag V Tag Data Data V Tag Data Data 253 **H** 253 254 254 **T** 254 254 □ 255 255 **T** 255 **T** 255 4x1 select

Hit

Proceedings of CPS&IoT2019 page 90

Data

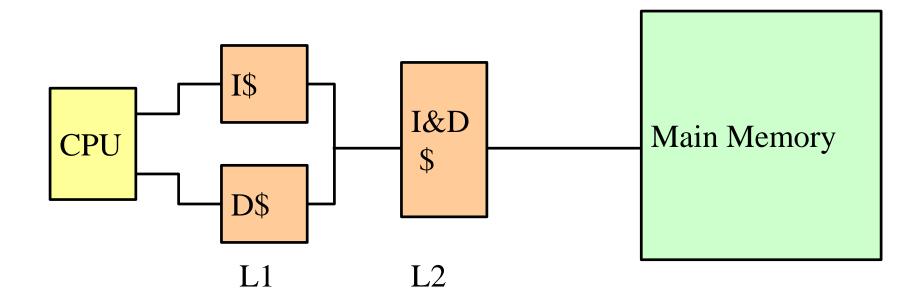

## Splitting first level cache, 2<sup>nd</sup> level cache

- Split Instruction and Data cache:

- Caches can be tuned differently

- Avoids dual ported cache

- 2<sup>nd</sup> Level: reduce miss penalty

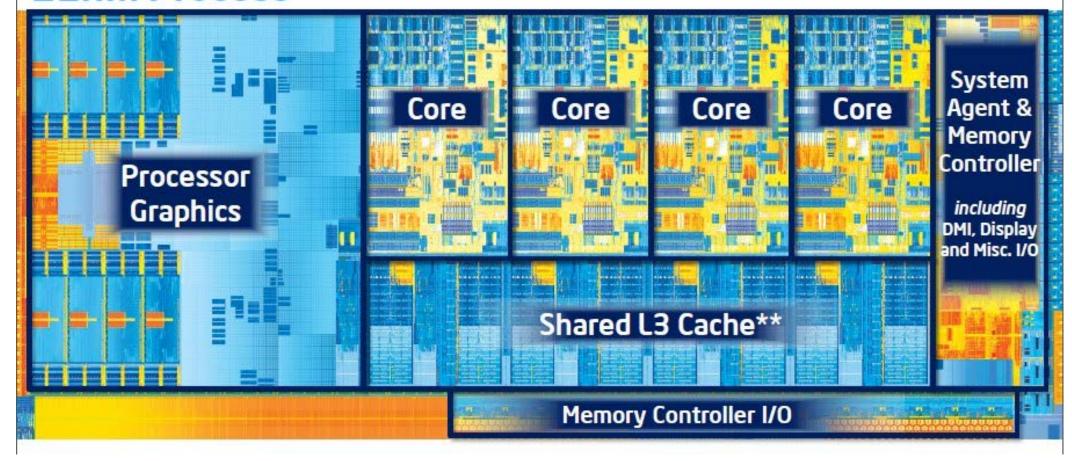

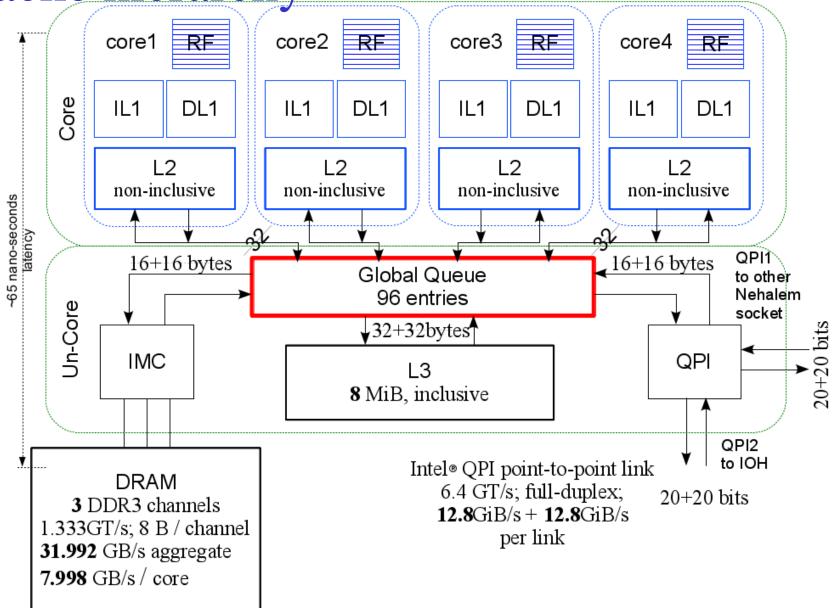

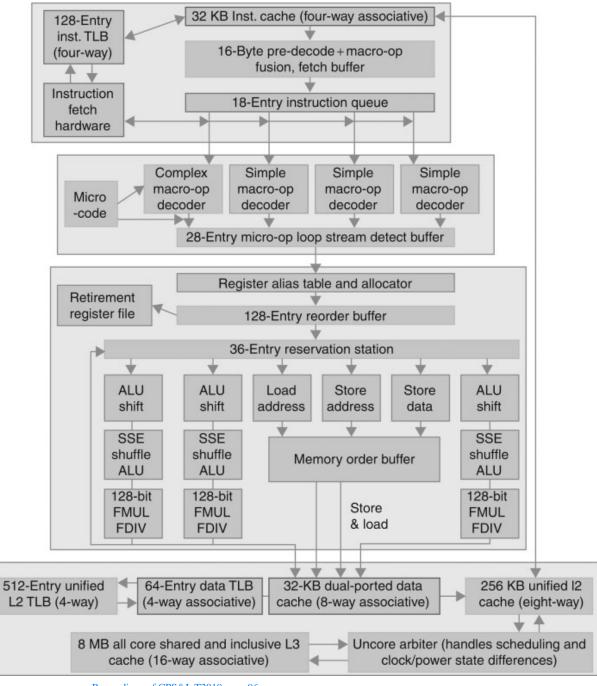

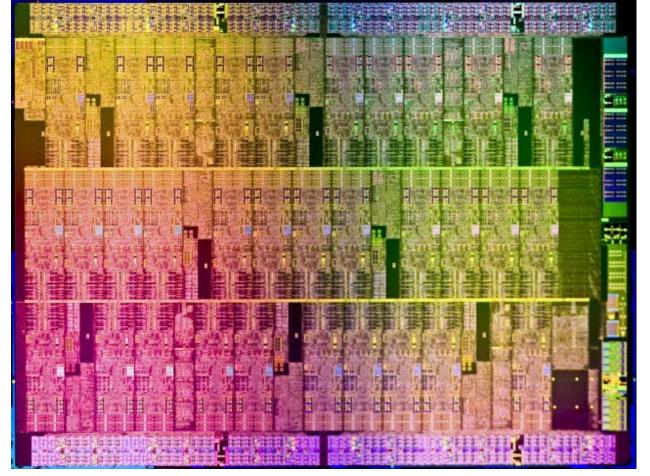

## Example Intel: i7 Ivy Bridge, 22 nm

# 3rd Generation Intel® Core™ Processor: 22nm Process

i7 (Nehalem) Cache hierarchy

- Per core

- L1 instruction

- L1 data

- L2 instr. + data

- Per 4 cores/die

- L3

Proceedings of CPS&IoT2019 page 93

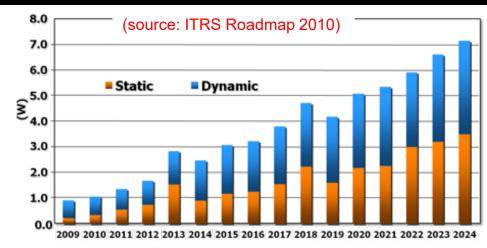

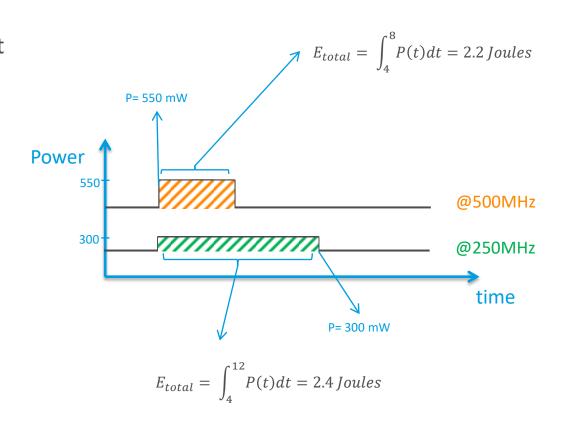

## Going parallel

- Why

- power gets out of control; Power =  $\alpha$  f C V<sup>2</sup> // frequency Capacitance Voltage<sup>2</sup>

- Many ways:

- More pipeline stages

- Multi-issue / Out-of-Order processing

- Multi-threading

- Vector or SIMD / SIMT GPU

- Multi-core: MIMD

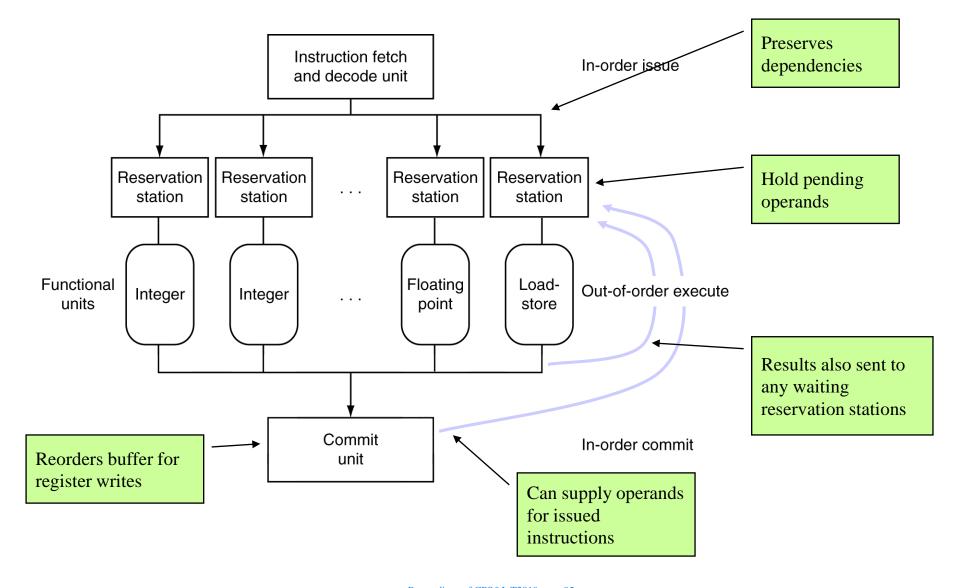

## OoO + Speculative execution

# Core i7 micro architecture

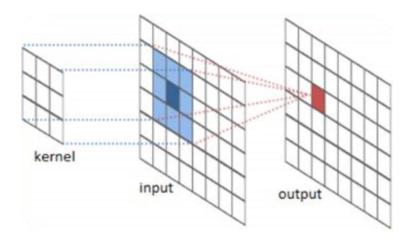

## SIMD concept

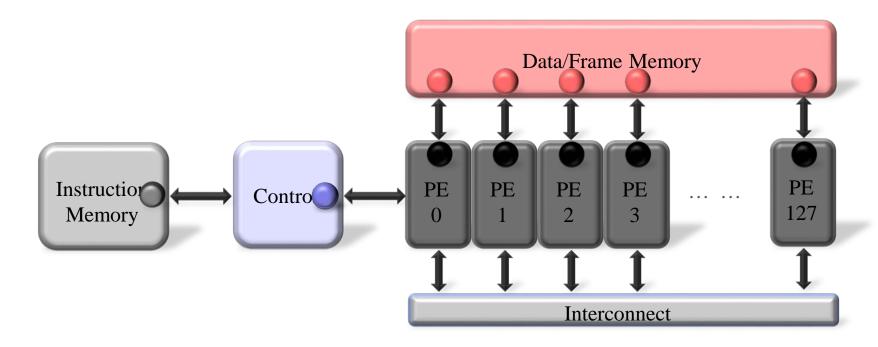

- ✓ SIMD: low-power architecture

- ✓ instruction fetch and decode overhead negligible

- ✓ massively-parallel: large number of PEs, high performance

- ✓ e.g. performing 128 'add' operations in 1 cycle

## SIMD Sub-word Implementations

- Implementations:

- Intel MMX (1996)

- Eight 8-bit integer ops or four 16-bit integer ops

- Streaming SIMD Extensions (SSE, 1999)

- Eight 16-bit integer ops

- Four 32-bit integer/fp ops or two 64-bit integer/fp ops

- Advanced Vector Extensions (AVX, 2010)

- Four 64-bit integer/fp ops or eight 32 bit integer/fp ops

- ARM NEON (since v6 architecture)

Operands must be consecutive and aligned memory locations

E.g. 16 bytes in parallel:

## Example 1: DAXPY, SIMD Code (MIPS)

• DAXPY = (double)  $Y = a \cdot X + Y$  //used to rank top500 supercomputers

```

L.D

F0, a

;load scalar a

MOV

F1, F0

; copy a into F1 for SIMD MUL

F2, F0

MOV

;copy a into F2 for SIMD MUL

F3, F0 ; copy a into F3 for SIMD MUL

MOV

R4,Rx,#512 ; last address to load (Double word immediate unsigned add)

DADDIU

Loop:

:load X[i], X[i+1], X[i+2], X[i+3]

L.4D

F4,0[Rx]

MUL.4D

;a\times X[i],a\times X[i+1],a\times X[i+2],a\times X[i+3]

F4,F4,F0

L.4D

F8,0[Ry]

;load Y[i], Y[i+1], Y[i+2], Y[i+3]

;a×X[i]+Y[i], ..., a×X[i+3]+Y[i+3]

ADD.4D

F8,F8,F4

S.4D

;store in Y[i],Y[i+1],Y[i+2],Y[i+3]

0[Ry],F8

Rx, Rx, #32

:increment index to X

DADDIU

DADDIU

Ry, Ry, #32

;increment index to Y

DSUBU

R20,R4,Rx

:compute bound

BNEZ

R20,Loop

; check if Idone CPS&IoT2019 page 99

```

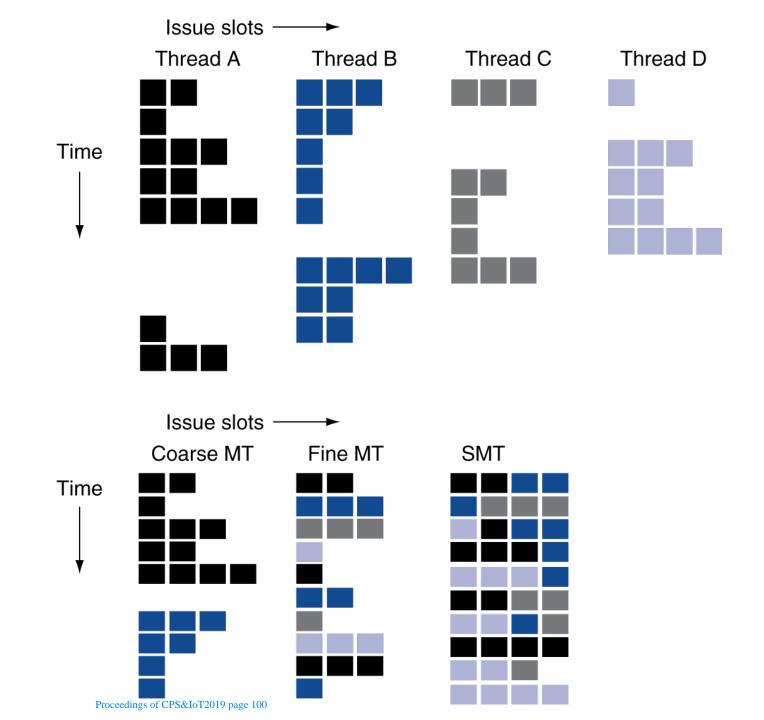

# Multi-Threading Options

4 Threadshiding latencies

## Going Multi-Core: from 2 to?

# Intel Xeon Phi count the number of cores!

### Major issues:

- 1. How to design

- 2. How to program?

- 3. How to communicate?

## Intel Xeon Phi

- Knights Landing (2015):

- build on Silvermont (Atom) x86 cores

- with 512-bit (SIMD) AVX units

- up to **72 cores / chip** => 3 TeraFlops

- 14 nm

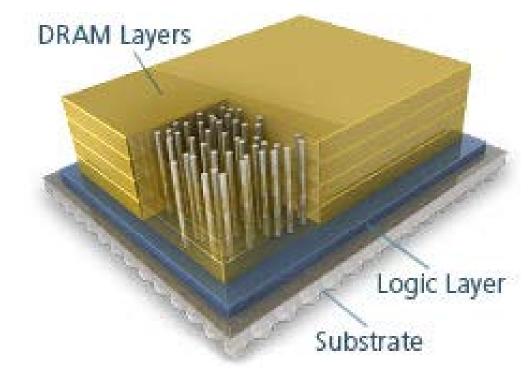

- using Micron's DRAM 3D techn.

(hybrid memory cube)

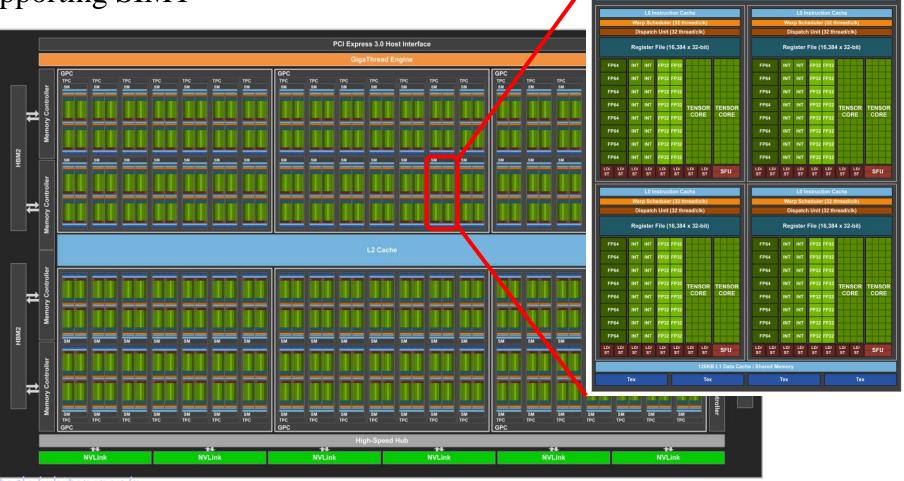

## GPUs: NVIDIA Volta (2017)

Combining MIMD + SIMD + MultiThreading

=> multiple SMs, supporting SIMT

https://images.nvidia.com/content/pdf/tesla/whitepaper/pascal-architecture-whitepaper.pdf

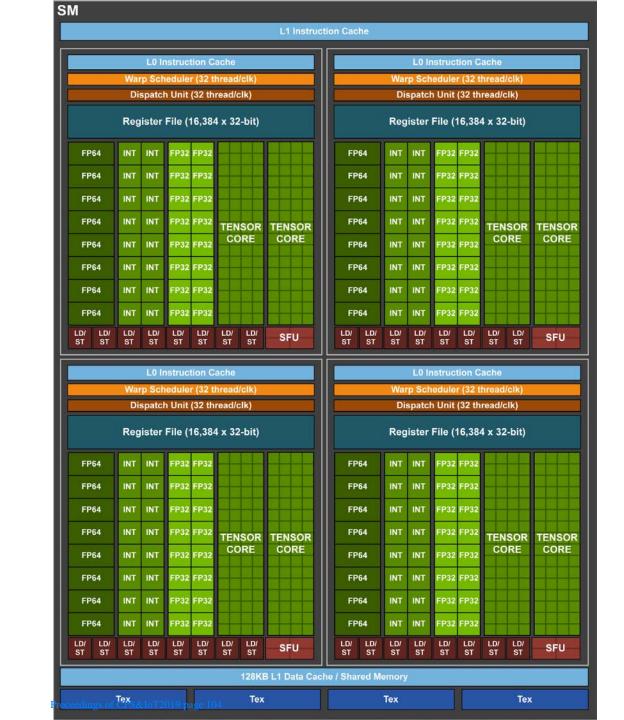

## 1 SM core

- Units:

- 8 tensor cores/SM

- 64 Int units

- 64 FP32

- 32 FP64

- 32 Ld/St

- 4 SFUs

- 128 LB L1 Data \$

- 4 warp schedulers

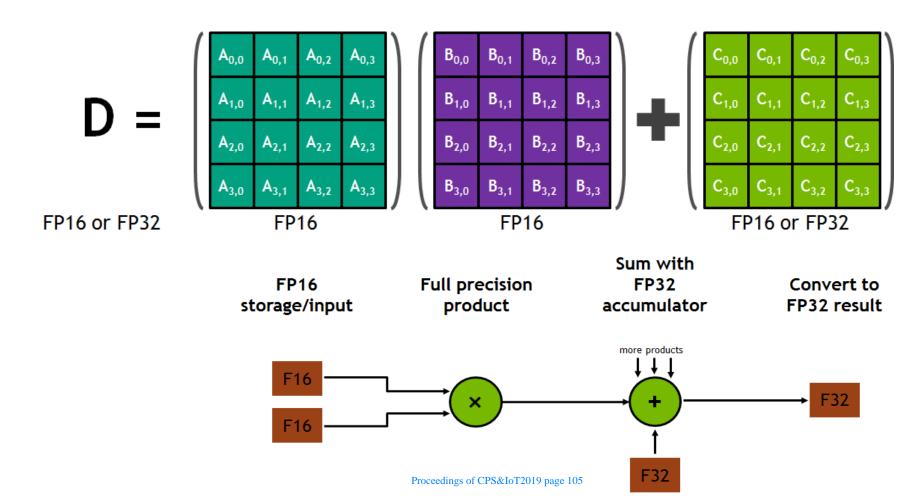

### Tensor core operation

- D = AxB + C, all 4x4 matrices

- 64 floating point MAC operations per clock

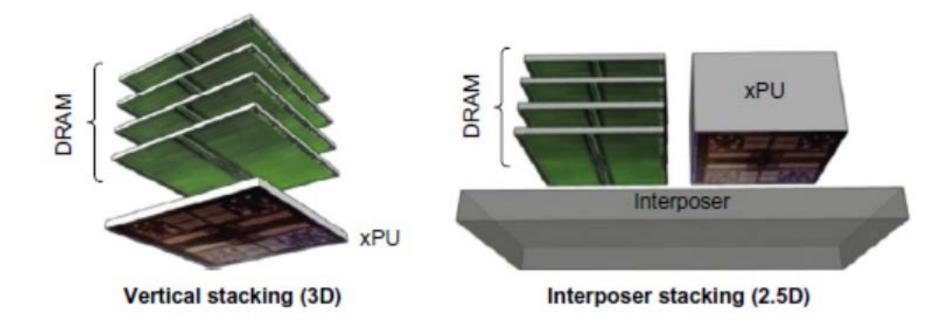

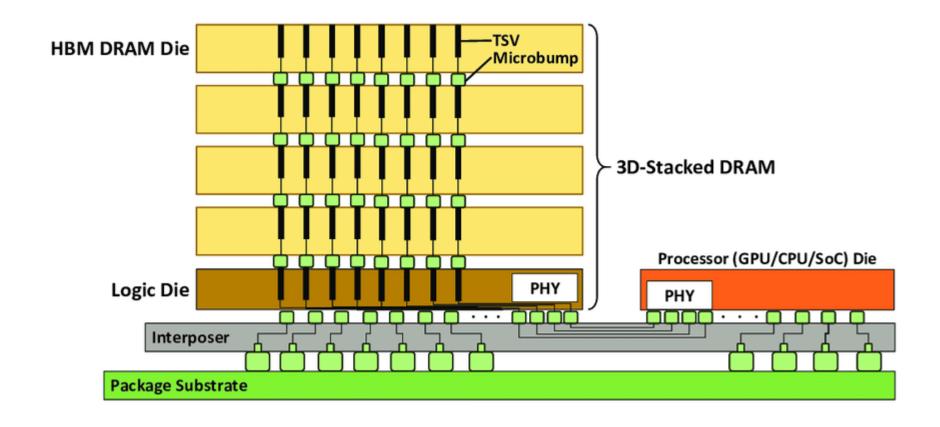

# Near-Memory Computing using Stacked DRAM: 2.5D vs 3D

- Stacked DRAMs in same package as processor

- High Bandwidth Memory (HBM)

# 2.5 D: using Interposer

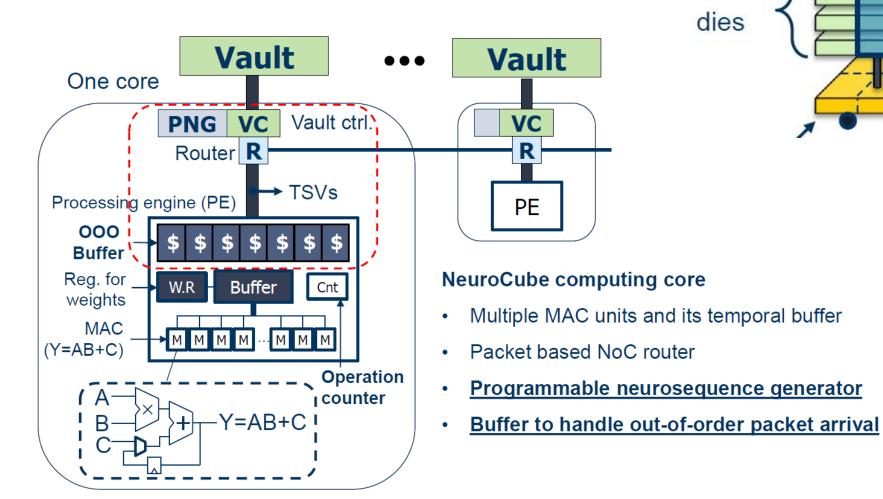

# 3D computing NeuroCube (ISCA 2016)

Vault

DRAM

Host

CPU

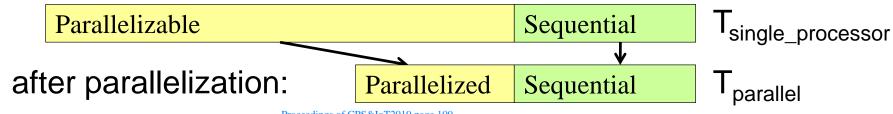

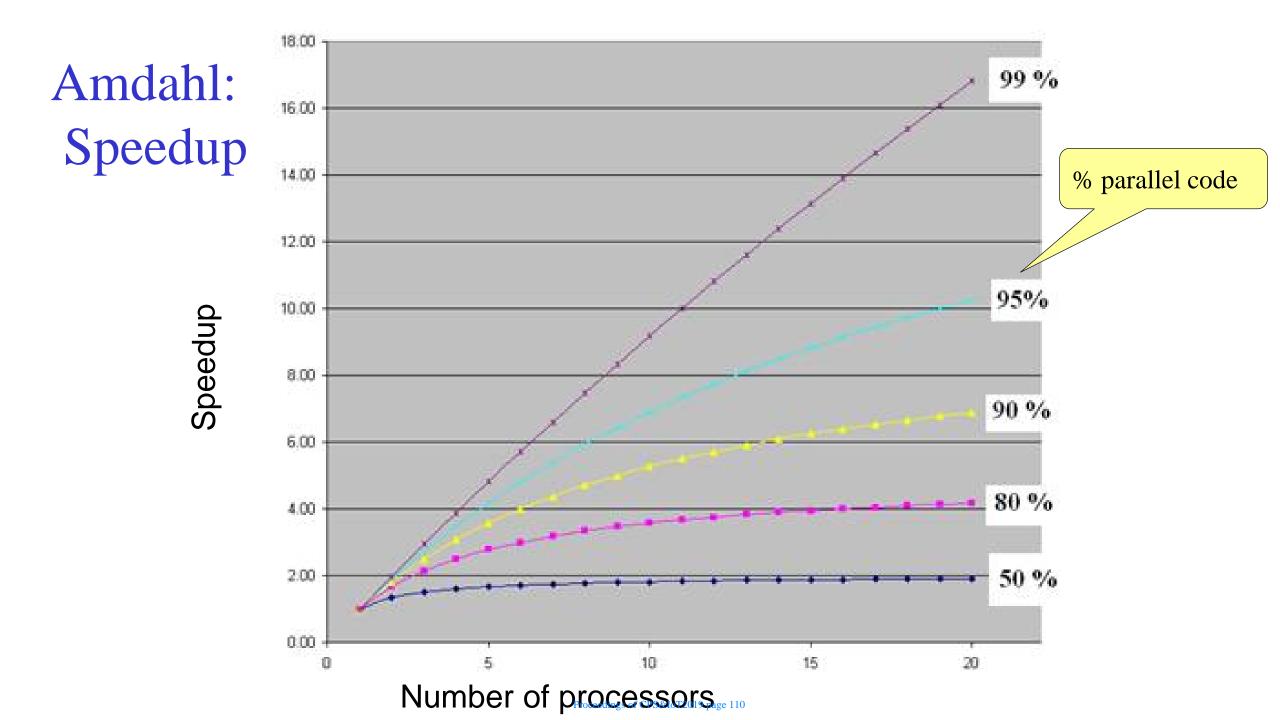

# Does it help? Amdahl's Law

- Sequential part limits speedup

- Example: P = 100 processors, can we get  $90 \times$  speedup?

$$- T_{parallel} = T_{parallel} / 100 + T_{parallelizable}$$

$$Speedup = \frac{1}{(1 - F_{parallelizable}) + F_{parallelizable}} / 100} = 90$$

$$=> F_{parallelizable} = 0.999$$

Need sequential part < 0.1% of original time

Proceedings of CPS&IoT2019 page 109

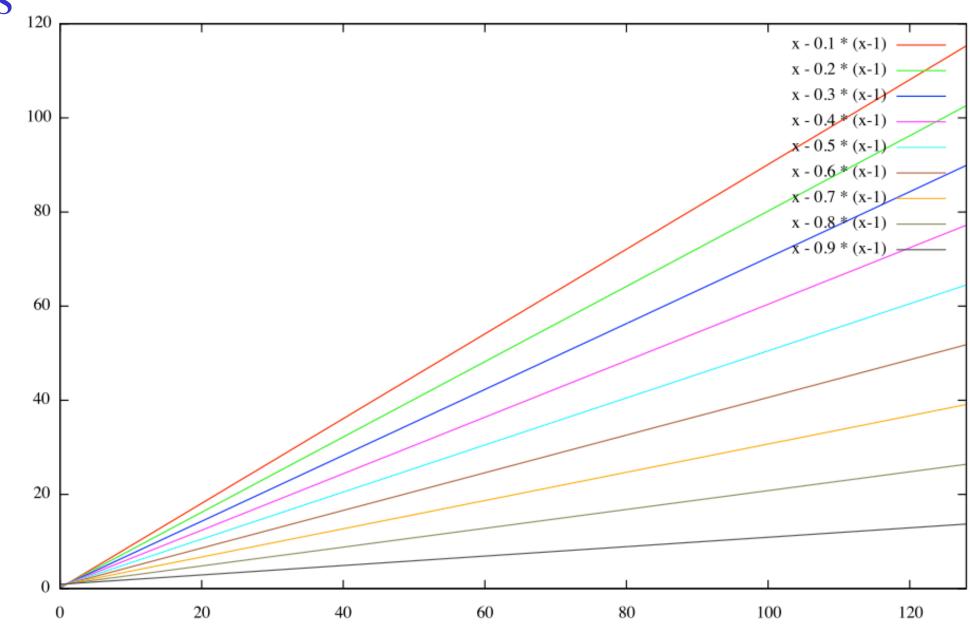

### Luckily we have Gustafson's law

• Amdahl's law: Strong scaling:

- Gustafson's law: Weak scaling

- Problem size grows proportional with number of processors. E.g.:

- 10 processors,  $10 \times 10$  matrix

- 100 processors, 32 × 32 matrix

- Constant performance in this example (derive the Speedup formula !!)

- Speedup =  $(P-1)f_{parallizable} + 1$

- Effectively: Linear speedup!!

Gustafson's scaling

Speedup - S(P)

Gustafson's Law: S(P) = P-a\*(P-1)

Proceedings of CPS&IoTNumber of Processors - P

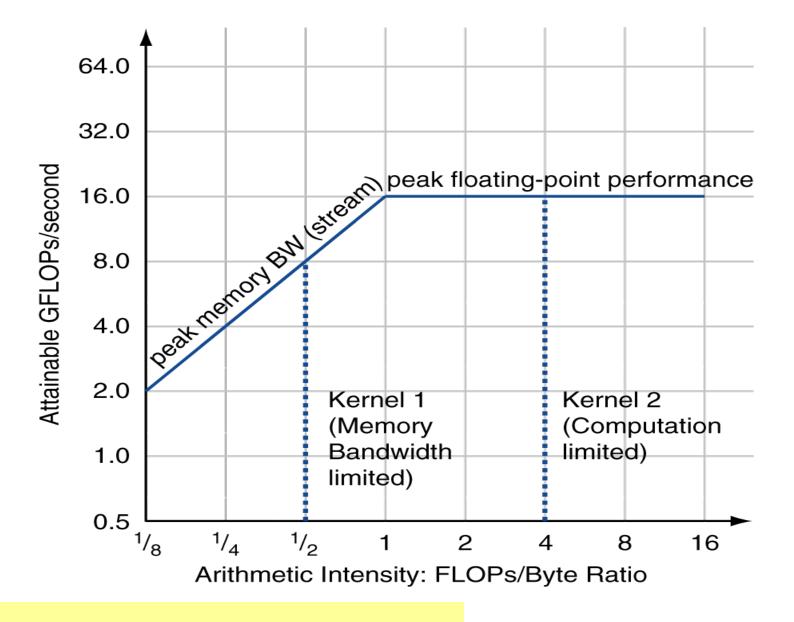

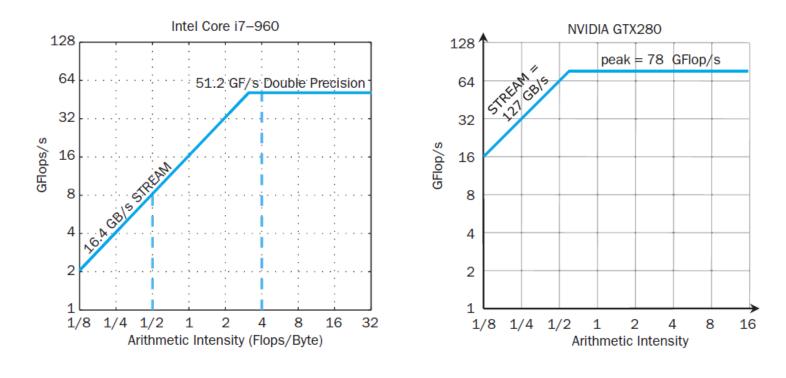

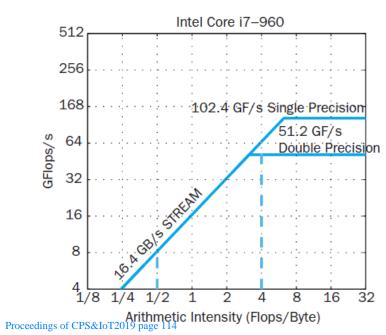

# Does it help? Check the Roofline

Attainable GPLOPs/sec =

Min (Peak Memory BW x Arithmetic Intensity, Peak FP Performance)

#### Rooflines

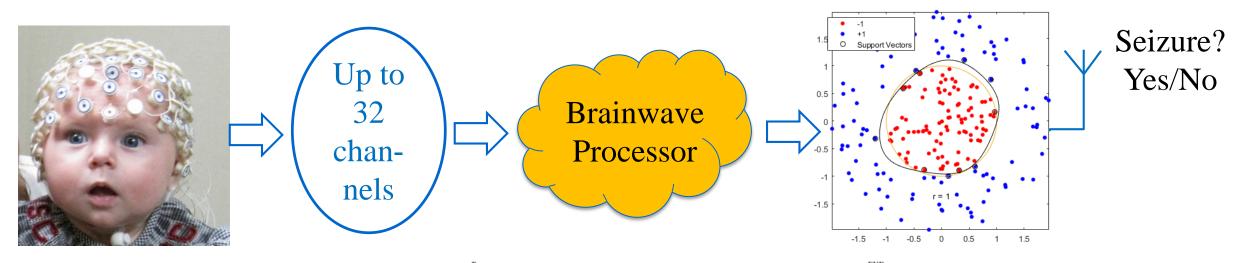

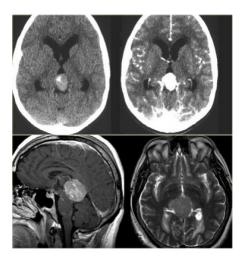

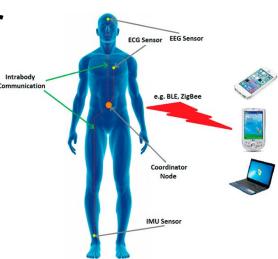

# Example CPS: EEG monitoring

5/23/2019 ECA H.Corporaal

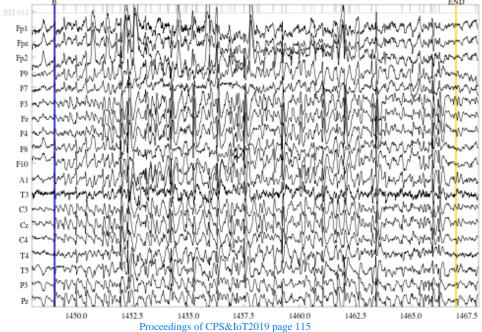

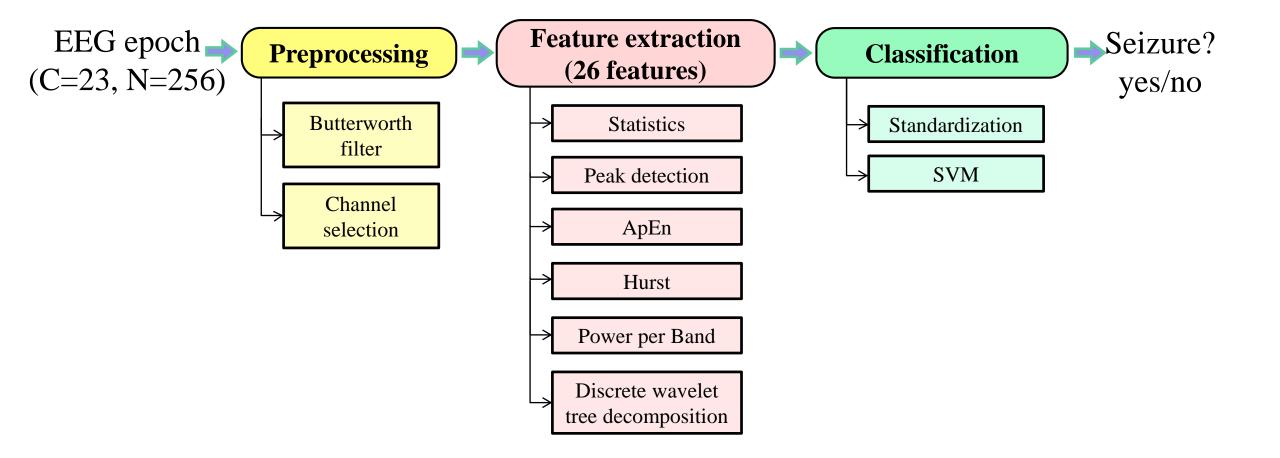

# EEG Processing steps

5/23/2019 ECA H.Corporaal Proceedings of CPS&IoT2019 page 116

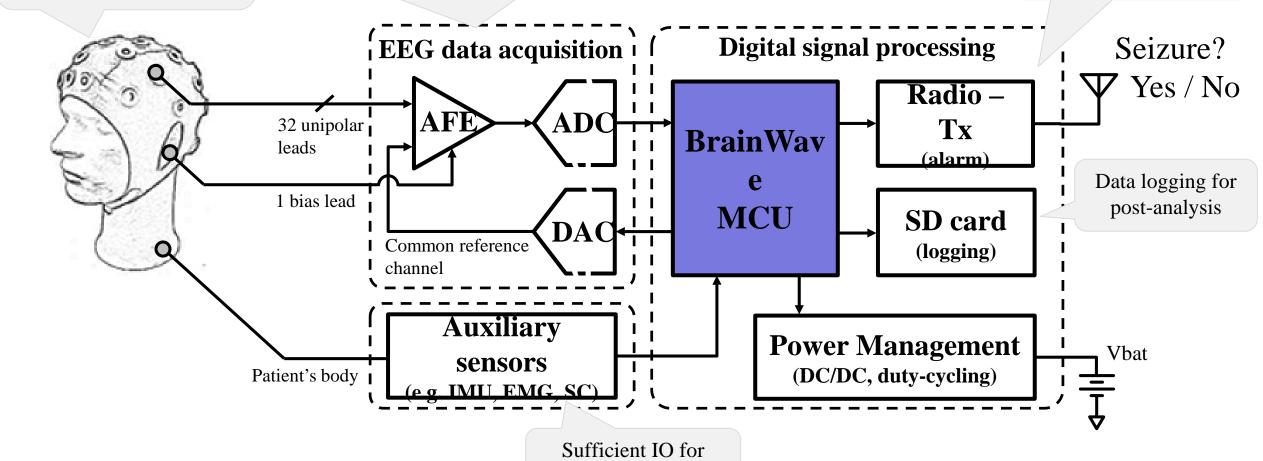

# Brainwave monitoring system – Overview

>24-channel scalp EEG cap with gel-based or dry electrodes

- Low noise amplifiers ( $<0.5\mu V_{RMS}$ ) with gain control

- >12-bit ADC precision (0.5µV resolution)

- >200Hz sampling rate (0.5Hz 100Hz) [1]

Wireless alarm to notify medical experts in case of emergency

Headset picture: TMSi Mobita

[1] IFCN standards for digital recording of clinical EEG – Nuwer et al. (1998)

supportive sensors

Proceedings of CPS&IoT2019 page 117

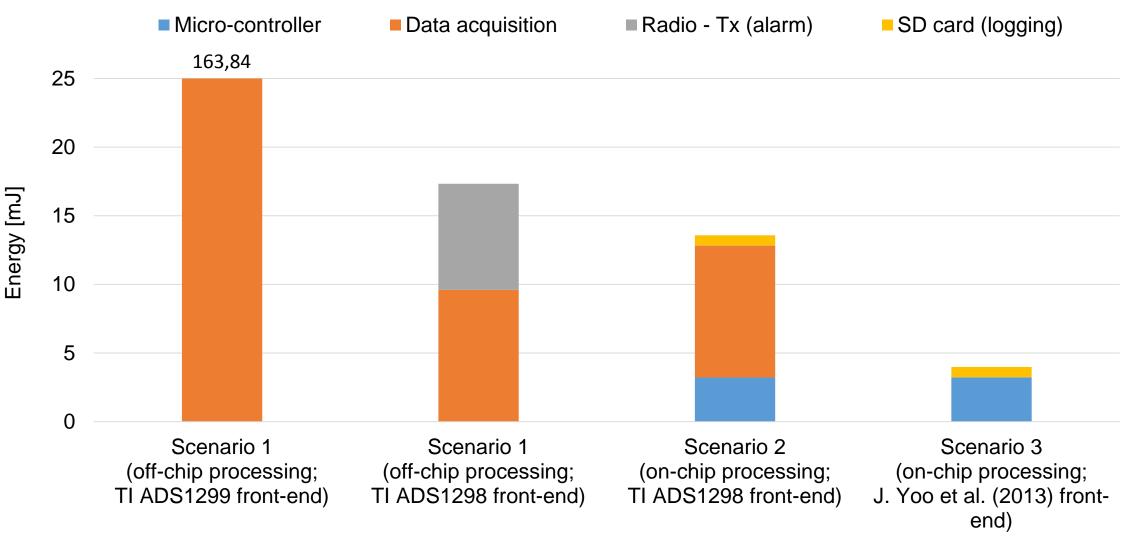

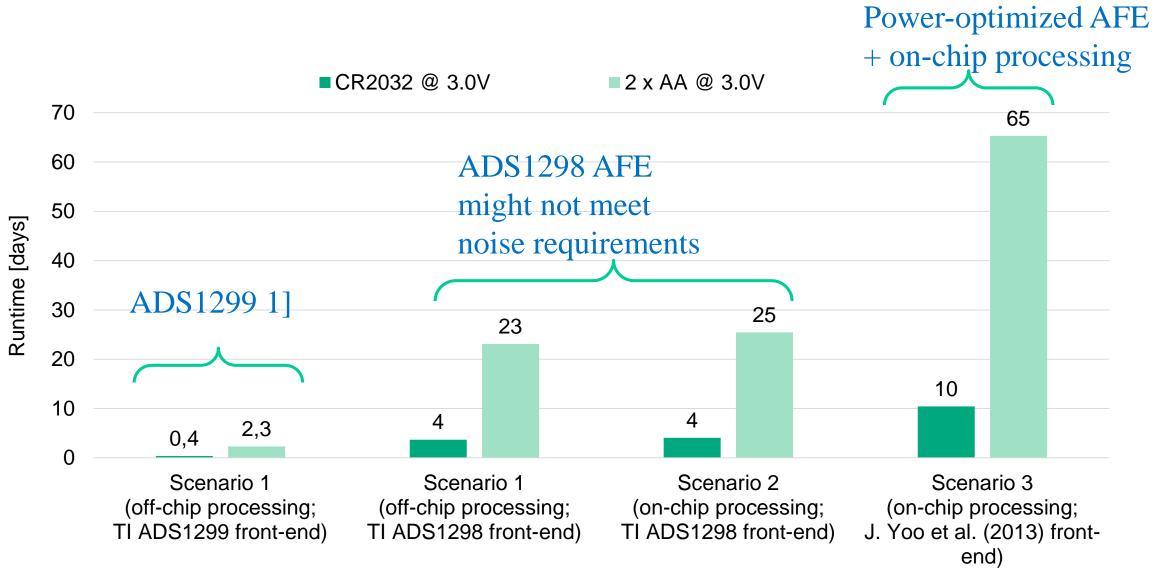

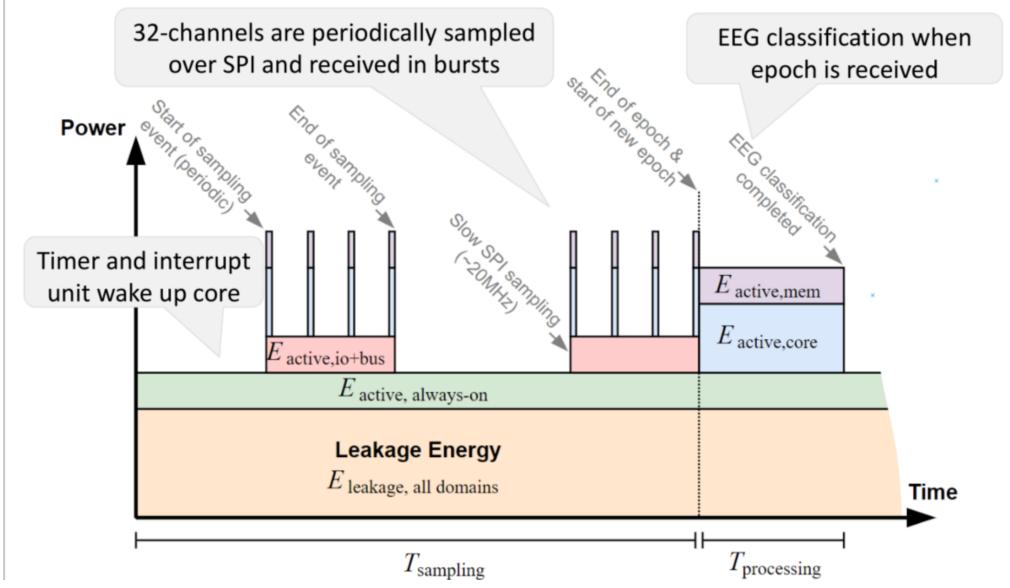

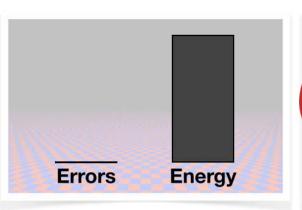

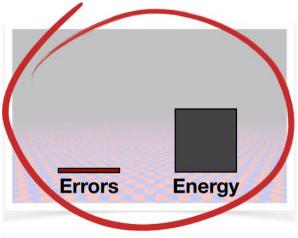

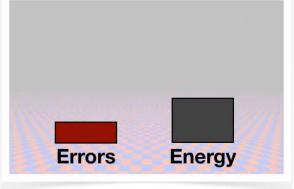

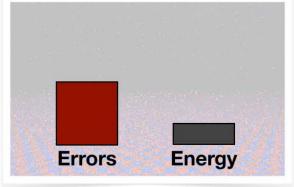

# Brainwave monitoring system – Energy breakdown

- Three system scenarios:

- 1. Off-chip processing; raw EEG data is transmitted to the nearest coordinator

- 2. On-chip seizure detection with standalone AFE + ADC; only small alarm is send

- 3. Identical to scenario 2 but with power-optimized on-chip AFE + ADC Putting a system together:

| Description       | Component                                                                                                                                    | Configuration 1 (off-chip processing)          | Configuration 2 & 3 (on-chip processing) |  |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------|--|

| Micro-controller  | STM32F401xB with ARM Cortex-M4                                                                                                               | Not used                                       | Active (Lei Wang et al. (2017))          |  |

| Data acquisition  | <ul> <li>TI ADS1299 AFE with 24-bit ADC</li> <li>TI ADS1298 AFE with 24-bit ADC</li> <li>J. Yoo et al. (2013) AFE with 10-bit ADC</li> </ul> | Continuous sampling of 32 EEG channels @ 100Hz |                                          |  |

| Radio – Tx        | Dialog DA14580 SoC with BLE 4 stack                                                                                                          | Send raw EEG data                              | Send alarm (256B per 20s)                |  |

| SD card (logging) | Sandisk microSD 16GB                                                                                                                         | Not used                                       | Store raw EEG data                       |  |

# BrainWave system overview energy breakdown

#### Estimated system energy breakdown per epoch

# EEG monitoring system – Battery runtime (days)

#### RISC-V runtime

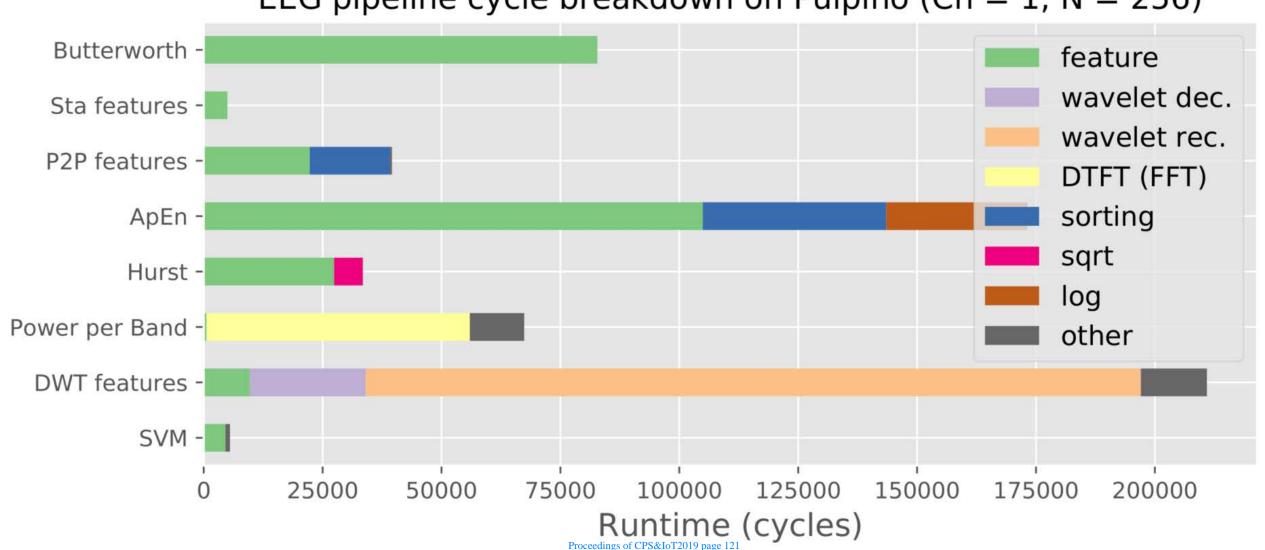

#### EEG pipeline cycle breakdown on Pulpino (Ch = 1, N = 256)

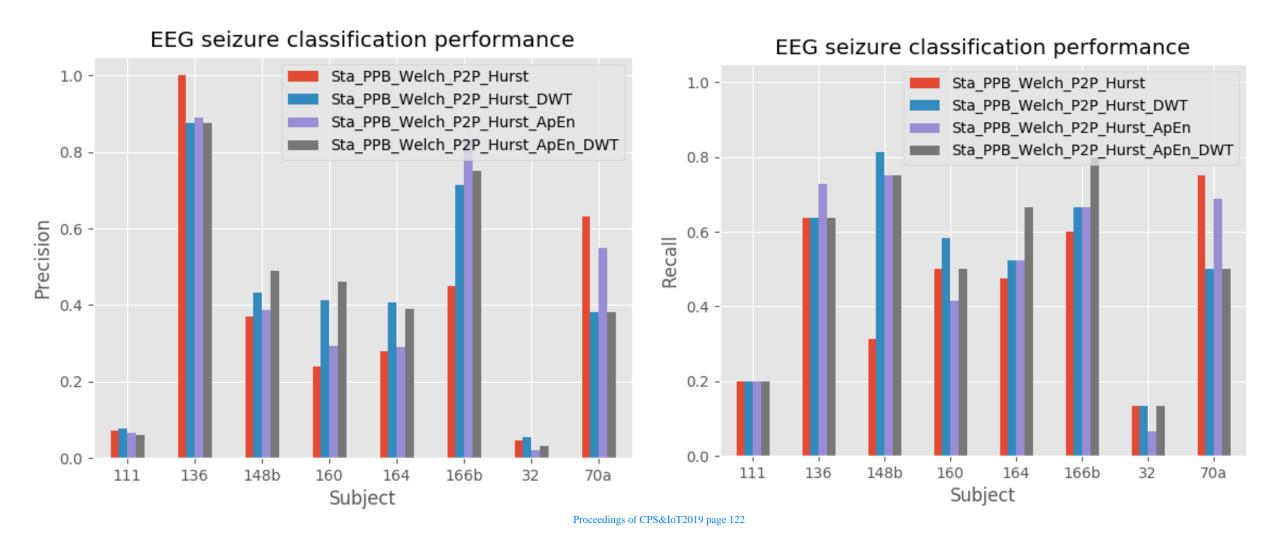

# Feature selection experiment

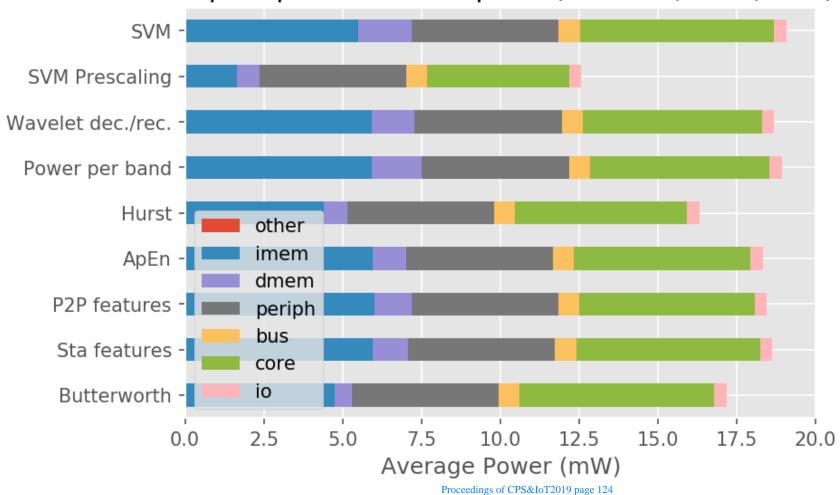

# Energy-efficiency RISCV only evaluation

# Energy-efficiency RISCV

• Energy/cycle roughly similar for all features on RISCV

Pulpino power consumption (400MHz, 1.0V, 25C)

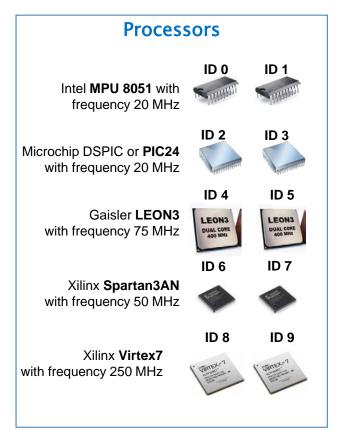

# Some CPS processors

- Arduino

- Rasberry-Pie

- RISC-V Pulpino

- Jetson nano

• Experimental: CGRA

- If you need advanced Deep Learning Networks, e.g.

- Intel Movidius

- Google: Edge TPU

- NVIDIA Xavier

- Newest Xilinx FPGA

- NVIDIA DLA (Open Source Verilog)

5/23/2019 ECA H.Corporaal Proceedings of CPS&IoT2019 page 125

#### Conclusions

- Many processor options, also for CPS

- Energy-efficiency is major problem

- All exploit parallelism

- many options

- Do not forget the memory hierarchy

- Compiler, mapping and optimization research needed!

- using local memories efficiently

- hitting the roofline

- Many MPSoCs and Development boards to get started

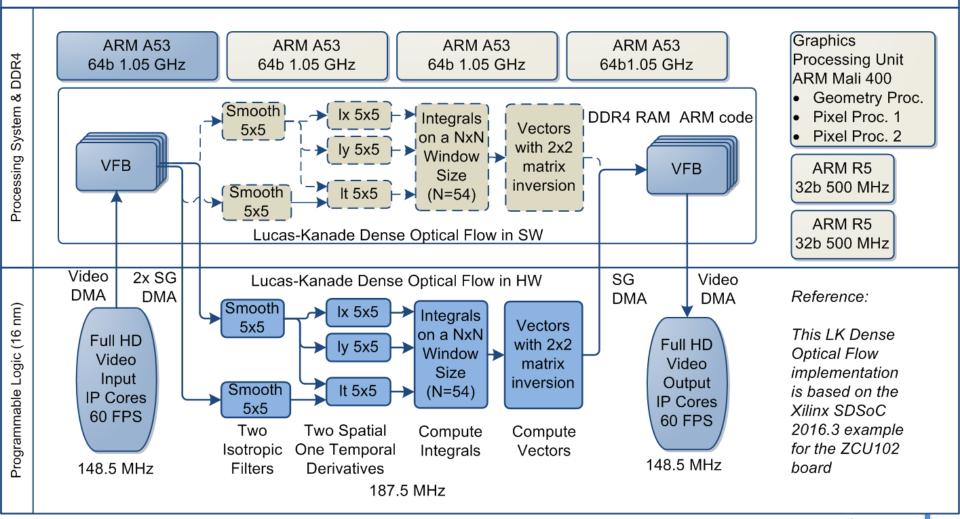

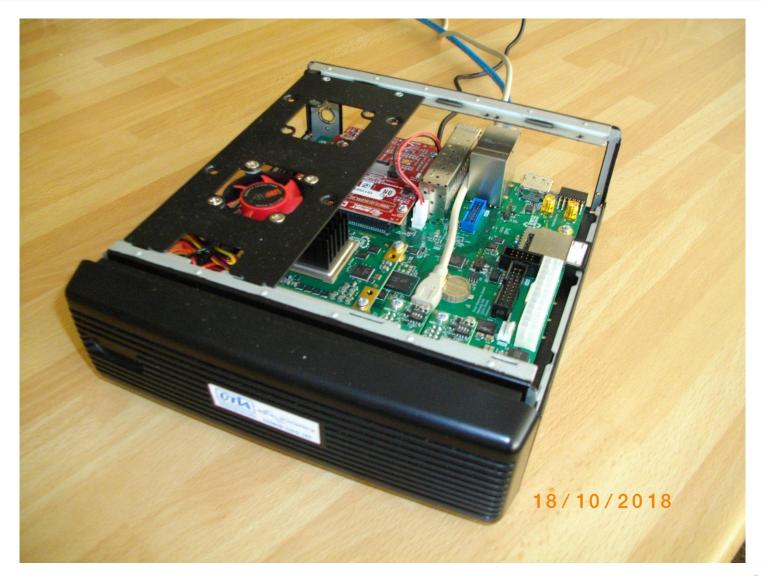

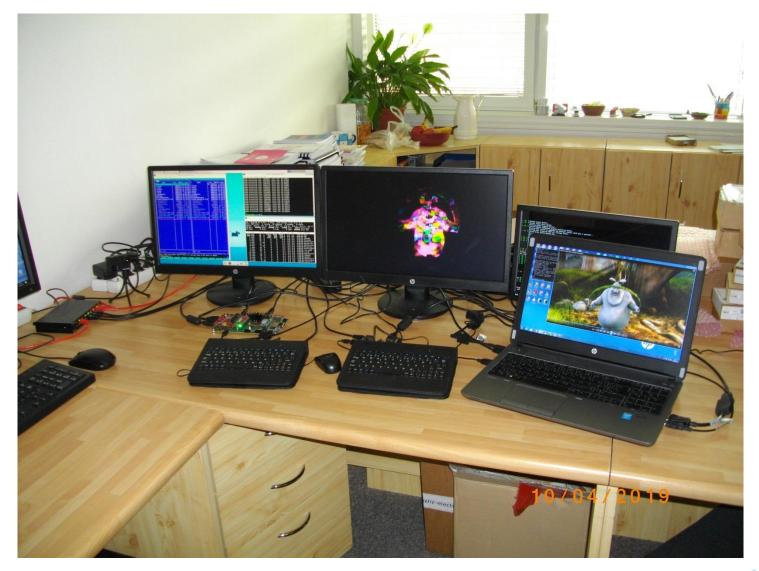

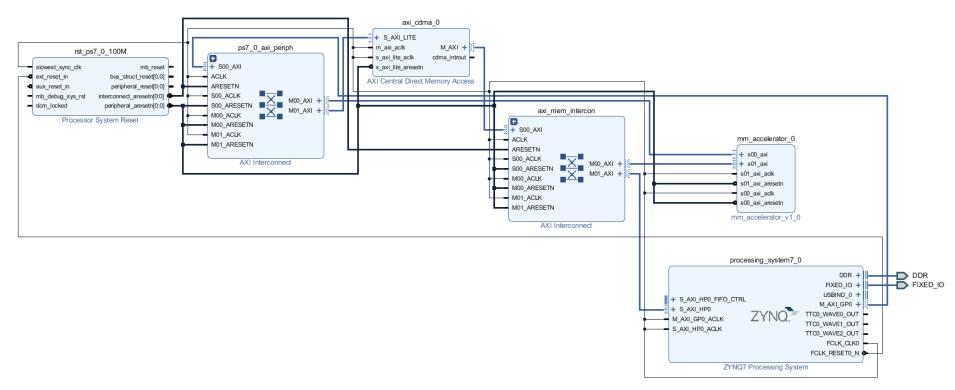

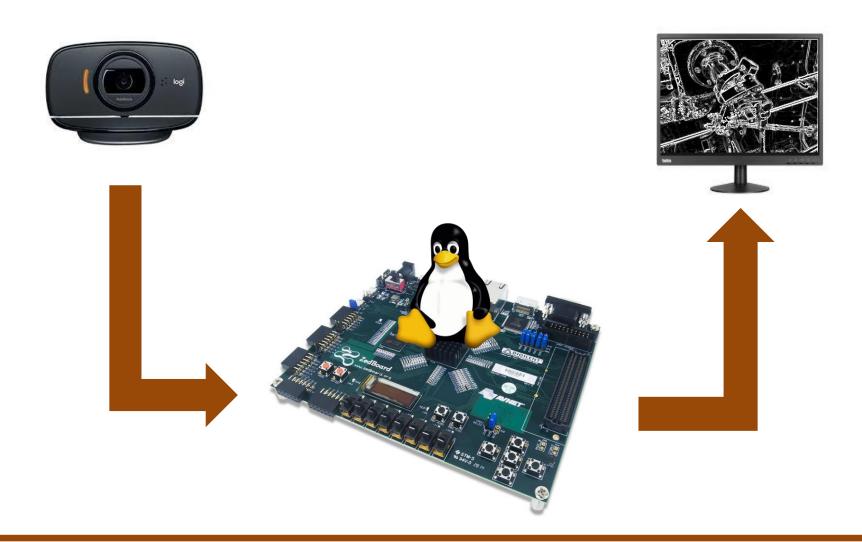

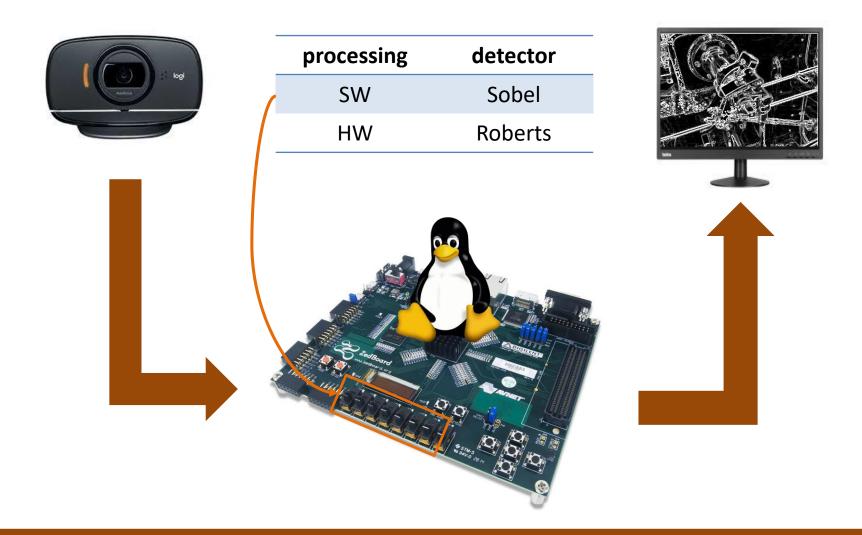

# Implementation of HW-accelerated video-processing on industrial Zynq modules

Jiří Kadlec, Zdeněk Pohl, Lukáš Kohout

// "From the cloud to the edge - smart IntegraTion and OPtimisation Technologies for highly efficient Image and VIdeo processing Systems" //

# ÚTIA AV ČR v.v.i.

<u>Jiří Kadlec</u>, Zdeněk Pohl, Lukáš Kohout

#### // Presentation Overview

- Introduction to the Xilinx SDSoC design flow

- Boards supported by UTIA in FitOptiVis:

- 2x A9, .5GB DDR3, .1Gb Eth ZynqBerry

- **UltraScale4x5** 4x A53, 2x R5, 2GB DDR4, 1Gb Eth

- UltraScale8x5 4x A53, 2x R5, 4GB DDR4, 1Gb Eth

- Example of acceleration LK Dense Optical Flow

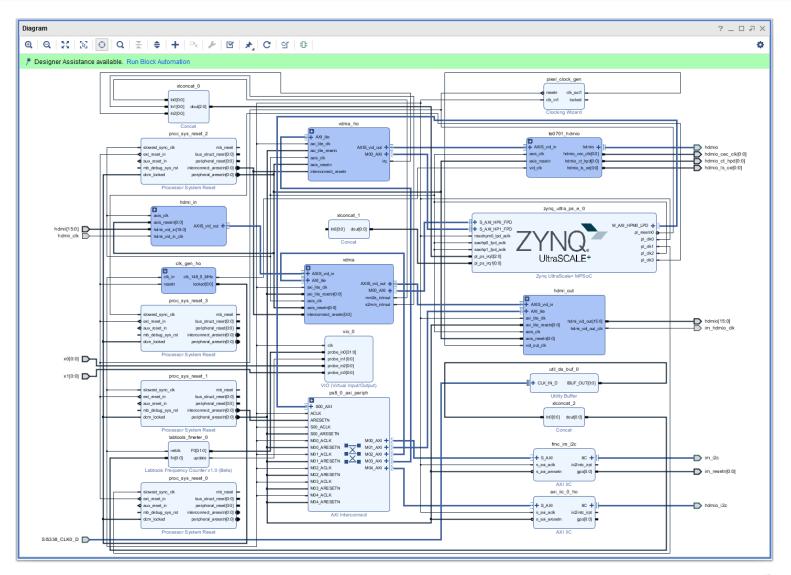

- Demonstration of board support platform generation project for Zyng Ultrascale+ module: TE0820-03-4EV-1EA on TE0701-06 carrier

- HW is from: https://www.trenz-electronic.de/

Proceedings of CPS&IoT2019 page 129

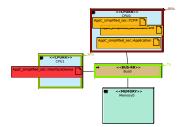

#### // What is Xilinx SDSoC System Lev. Compiler?

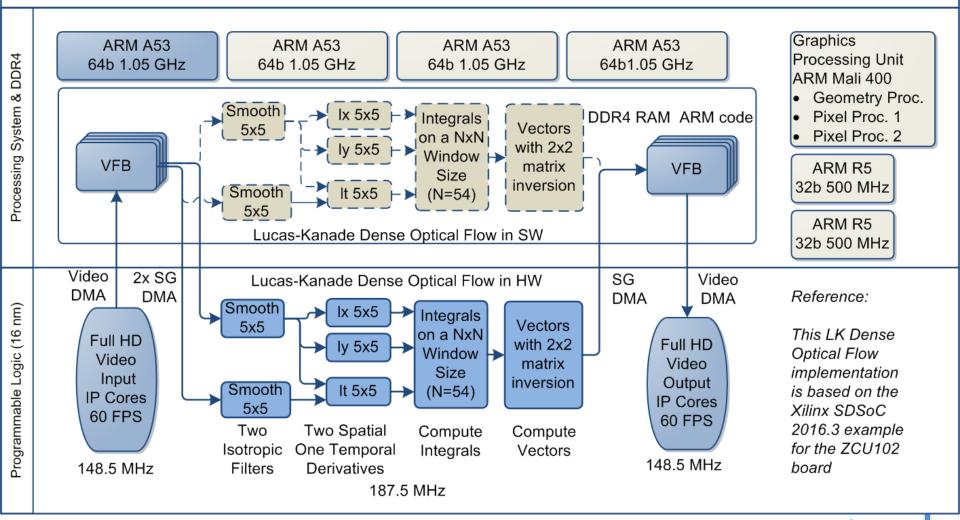

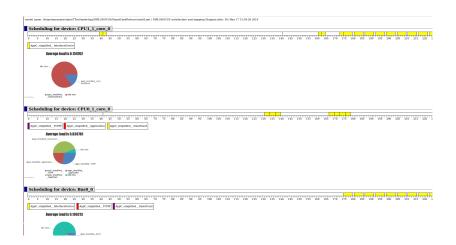

#### LK Dense Optical Flow on Xilinx Zynq Ultrascale (SDSoC 2017.4)

#### // ZynqBerry

#### 8.5 cm x 5.5 cm x 2 cm

####

#### // UltraScale8x5 7.6 cm x 5.2 cm x 4.0 cm

#### // Comparison: PL size, Acceleration by HW

| Supported module     | Logic Cells<br>(K) | Memory<br>(Mb) | DSP<br>Slices | GPU        | VCU        | Ultra<br>RAM |

|----------------------|--------------------|----------------|---------------|------------|------------|--------------|

| ZynqBerry            | 28                 | 2.1            | 80            |            |            |              |

| <u>UltraScale4x5</u> | <u>192</u>         | <u>18.5</u>    | 728           | <u>YES</u> | <u>YES</u> | <u>YES</u>   |

| UltraScale8x5        | 747                | 57.7           | 3528          | YES        |            | YES          |

| int 32 Z[n,n] =<br>A[n,n]*B[n,n] |           | ARM<br>clock MHz | Accelerator clock MHz | Acceleration relative to ARM |

|----------------------------------|-----------|------------------|-----------------------|------------------------------|

| ZynqBerry                        | [18,18]   | 650              | 100                   | 5 x                          |

| <u>UltraScale4x5</u>             | [80,80]   | <u>1200</u>      | _200                  | <u>21 x</u>                  |

| UltraScale8x5                    | [250,250] | 1050             | 187                   | <b>101</b> x                 |

#### // Supported UltraScale5x4 Modules

| UltraScale4x5 TE0820 module | Xilinx UltraScale<br>Device | Logic<br>Cells<br>(K) | PL<br>Mem<br>(Mb) | PL<br>DSP<br>Slices | A53,<br>GPU,<br>VCU | DDR4<br>(GB) | Mod.<br>Price<br>(Euro) |

|-----------------------------|-----------------------------|-----------------------|-------------------|---------------------|---------------------|--------------|-------------------------|

| 02-2CG-1EA                  | xczu2cg-sfvc784-1-e         | 103                   | 5.3               | 240                 | 2,n,n               | 1            | 269                     |

| 02-3CG-1EA                  | xczu3cg-sfvc784-1-e         | 154                   | 7.6               | 360                 | 2,n,n               | 1            | 319                     |

| 02-4CG-1EA                  | xczu4cg-sfvc784-1-e         | 192                   | 18.5              | 728                 | 2,n,n               | 1            | 549                     |

| 02-2EG-1EA                  | xczu2eg-sfvc784-1-e         | 103                   | 5.3               | 240                 | 4,y,n               | 1            | 299                     |

| 02-3EG-1EA                  | xczu3eg-sfvc784-1-e         | 154                   | 7.6               | 360                 | 4,y,n               | 1            | 369                     |

| <u>03-4EV-1EA</u>           | xczu4ev-sfvc784-1-e         | <u>192</u>            | <u>18.5</u>       | <u>728</u>          | <u>4,y,y</u>        | <u>2</u>     | <u>669</u>              |

- Modules & PCBs are produced & distributed by:

- Trenz Electronic <a href="https://www.trenz-electronic.de/">https://www.trenz-electronic.de/</a>

- Carrier PCBs: TE0726-03, TE0701-06, TEBF0808-04A

- Immageon FMC adapter (HDMI I/O) is from Avnet

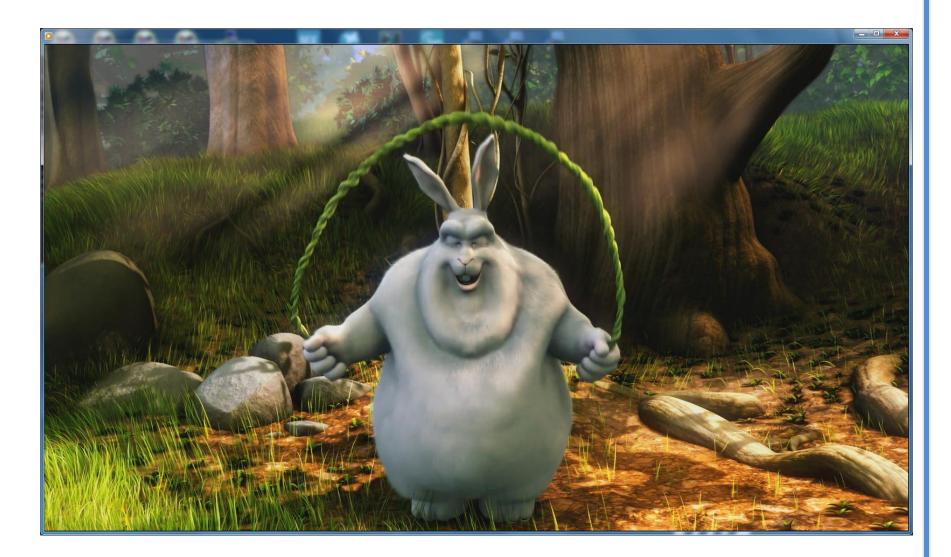

# // LK Dense Optical Flow Full HD – PC hdmi

#### // LK Dense Optical Flow Full HD 495x faster

#### // Create and compile Vivado 2018.2 project

- Create Windows setup \_create\_win\_setup.cmd

- Create virtual drive X: \_use\_virtual\_drive.cmd

- Create initial design in Vivado 2018.2

x:\zusys\vivado\_create\_project\_guimode.cmd

- Compile design to bitstream and HDF file

TE::hw\_build\_design -export\_prebuilt

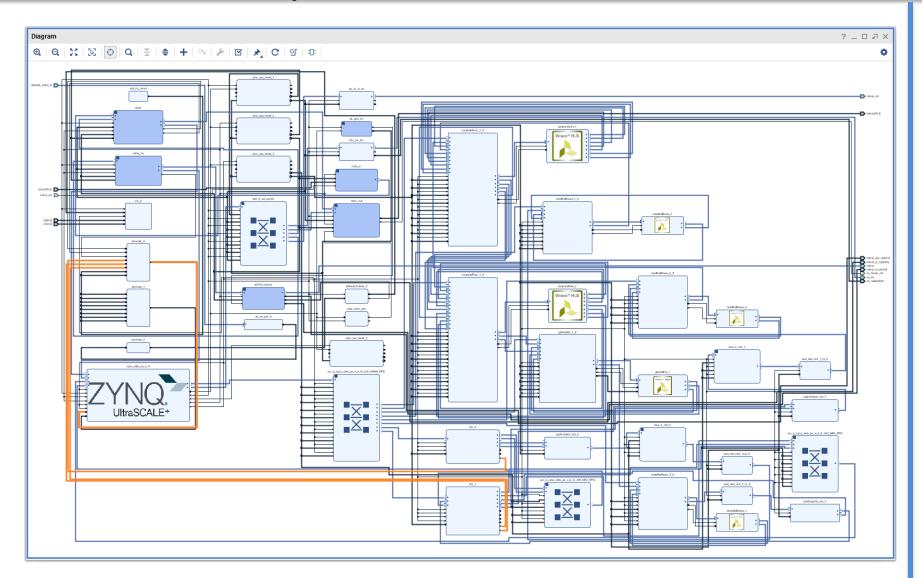

#### // Created initial Vivado 2018.2 design

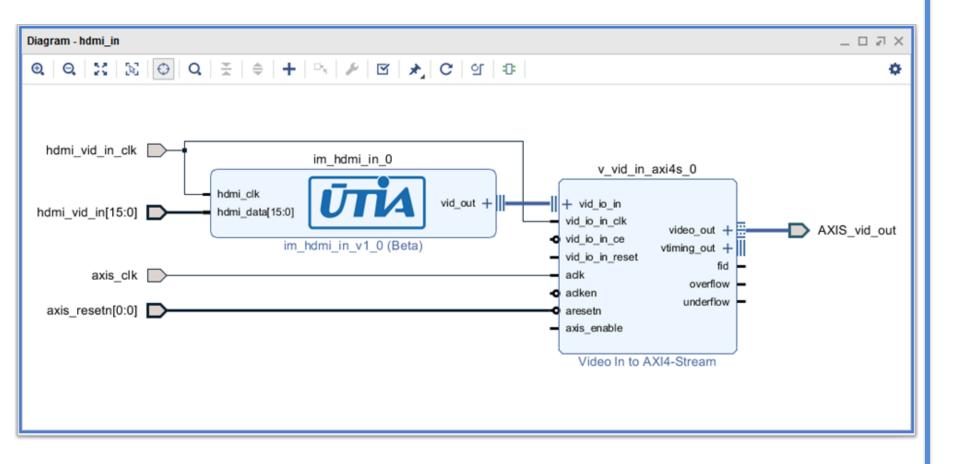

#### // HDMI\_in FULL HD HDMI video input

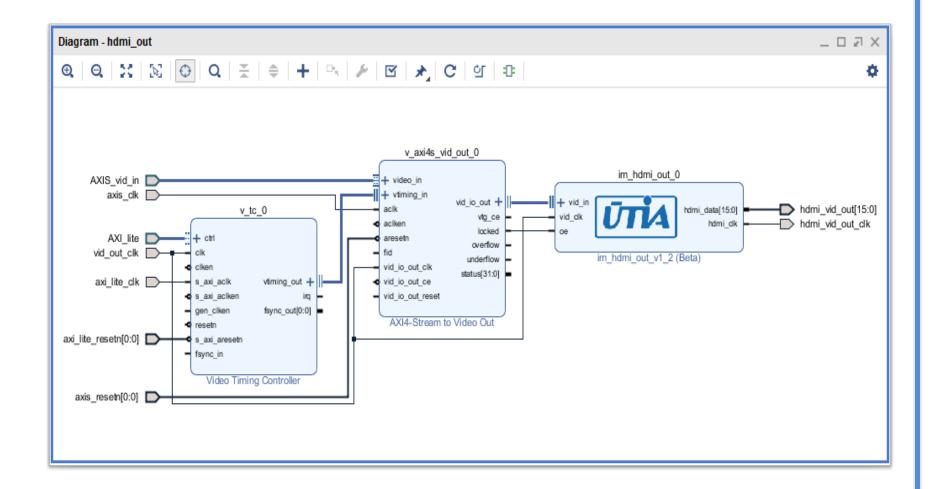

### // HDMI\_in FULL HD HDMI video output

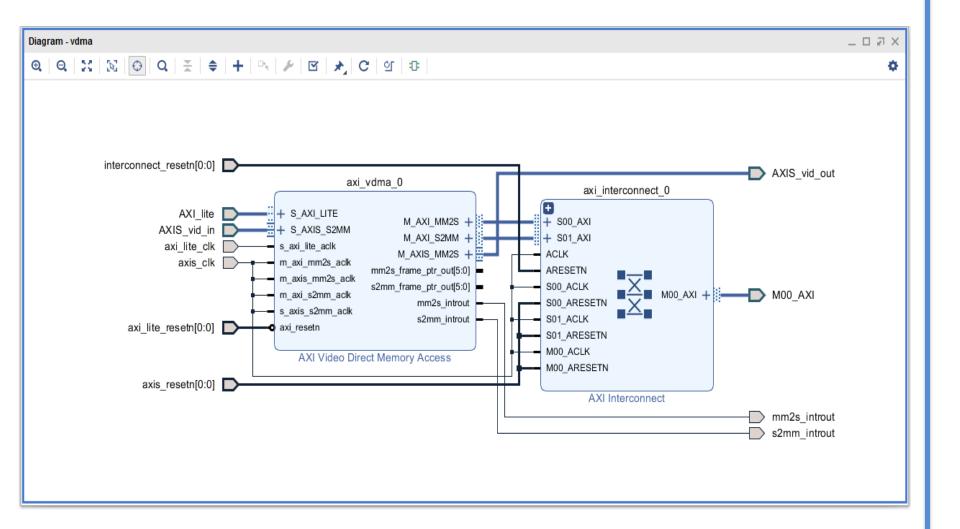

#### // Video DMA to 8 video frame buffers

#### // SDSoC 2018.2 Platform and Design Flow

#### LK Dense Optical Flow on Xilinx Zynq Ultrascale (SDSoC 2017.4)

#### // Configuration of PetaLinux 2018.2

Use of Vivado HDF in PetaLinux 2018.2

```

petalinux-config --get-hw-description=

/home/devel/work/TS82/TE0820/zusys/prebuilt/hardware/4ev_1e

```

Root filesystem type for Debian platform earlycon clk\_ignore\_unused root=/dev/mmcblk1p2 rootfstype=ext4 rw rootwait quiet

- Compile Petalinux 2018.2

petalinux-build

- Make Debian 9.8 "Stretch" sudo ./mkdebian.sh

- Zip created te0820-debian.img (7 GB)

zip te0820-debian te0820-debian.img

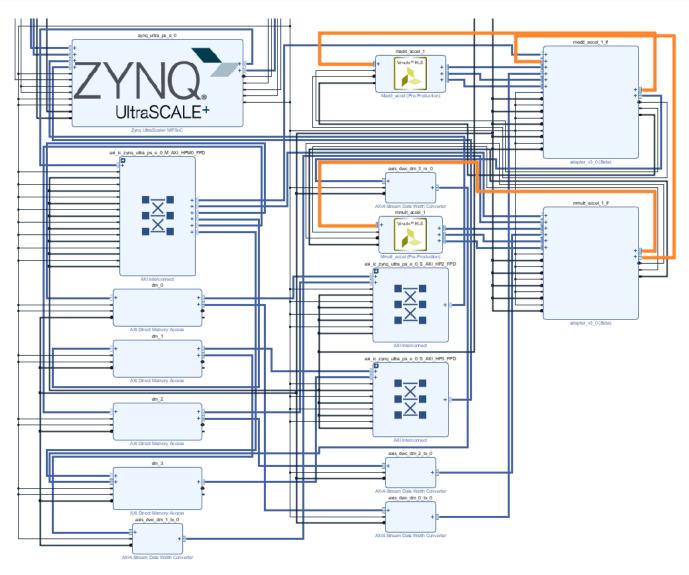

### // Create SDSoC 2018.2 platform from Vivado

Generate FSBL and BOOT.bin

TE::sw\_run\_hsi

Generate SDSoC platform

TE::ADV::beta\_util\_sdsoc\_project

In SDSoC 2018.2, compile example performing int32 matrix operation:

D[75,75] = A[75,75] \* B[75,75] + C[75,75]

X:\4EV-1EA\zusys\samples\z\_is\_a\_times\_b\_direct\_connect\

In SDSoC 2018.2, compile example LK Dense Optical Flow

# // Matrix Mult and Add [75x75]: 33x faster

### // LK Dense Optical Flow Full HD 495x faster

#### // FitOptiVis Design Time Resources

- FitOptiVis www:

- https://fitoptivis.eu/

- Resources on UTIA FitOptiVis www:

- http://sp.utia.cz/index.php?ids=projects/fitoptivis

- Detailed App. Note and Eval package:

Jiři Kadlec, Zdeněk Pohl, Lukáš Kohout: Design Time

and Run Time Resources for Zynq Ultrascale+

TE0820-03-4EV-1E with SDSoC 2018.2 Support

- Contact: Jiří Kadlec, UTIA AV CR v.v.i. <a href="http://zs.utia.cas.cz/">http://zs.utia.cas.cz/</a> kadlec@utia.cas.cz/

# Dataflow-Based Toolchain for Adaptive Hardware Accelerators

Francesca Palumbo<sup>1</sup>, Claudio Rubattu<sup>1,2</sup>, Carlo Sau<sup>3</sup>, Tiziana Fanni<sup>3</sup>, Luigi Raffo<sup>3</sup>

<sup>1</sup>University of Sassari, Intelligent system DEsign and Application (IDEA) Group

<sup>2</sup>University of Rennes, INSA Group

<sup>3</sup>University of Cagliari, Diee – Microelectronics and Bioengineering (EOLAB) Group

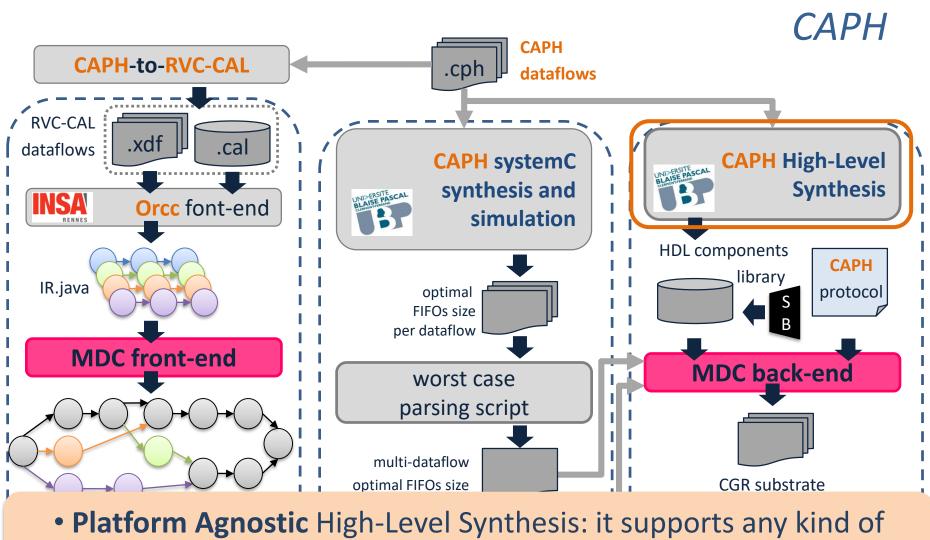

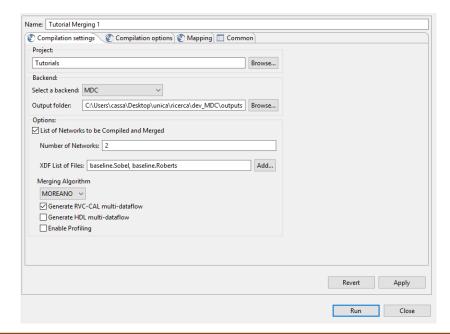

#### **MDC** suite

**Motivations and Overview**

# Who and Where

# Who and Where

# Who and Where

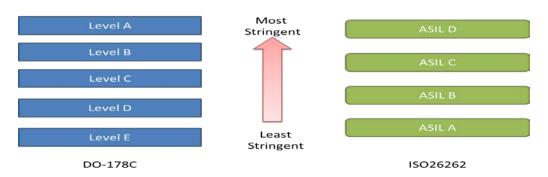

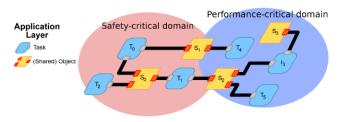

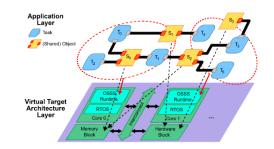

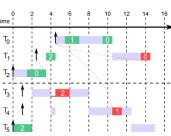

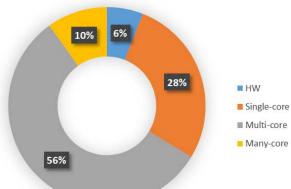

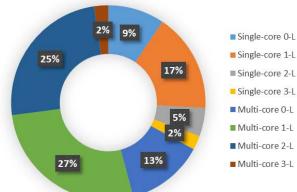

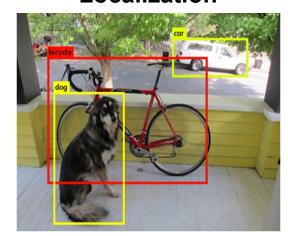

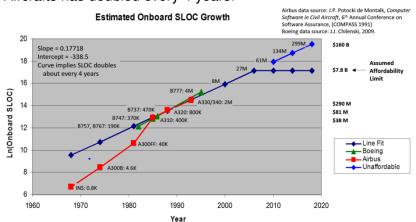

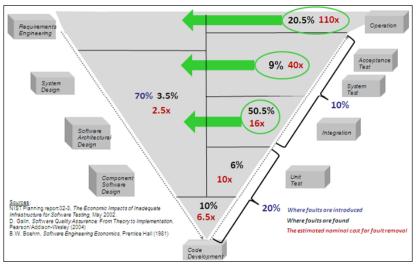

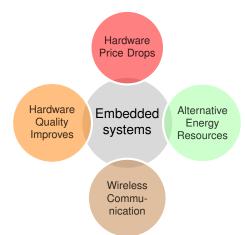

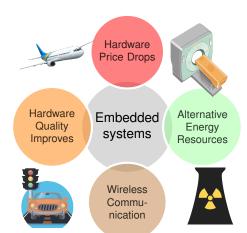

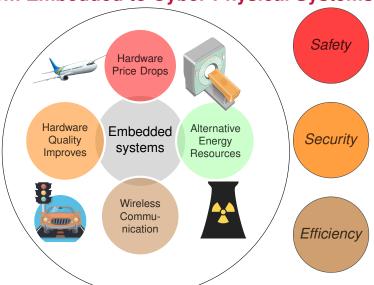

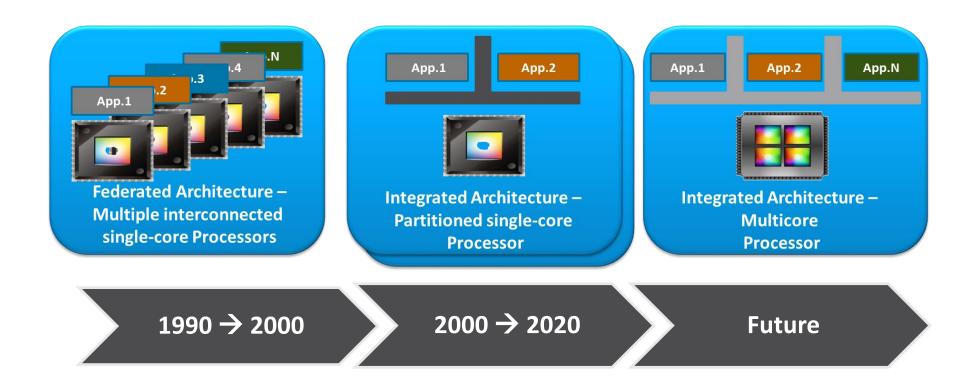

# Modern Embedded Systems

Embedded Systems (*real-time* computing systems with a dedicated functionality) are pervasive (98% of computers are embedded) and may present sensing and actuating capabilities.

# Modern Embedded Systems

Embedded Systems (*real-time* computing systems with a dedicated functionality) are pervasive (98% of computers are embedded) and may present sensing and actuating capabilities.

|            | Safety | Security | Certif. | Distrib. | НМІ | Seamless | MPSoC | Energy |

|------------|--------|----------|---------|----------|-----|----------|-------|--------|

| Automotive | x      | X        | X       | х        | X   | X        | X     |        |

| Aerospace  | х      | х        | х       | х        | х   |          | х     | х      |

| Healthcare | х      | х        | х       | х        | х   | х        | х     | х      |

| Consumer   |        |          |         |          | х   | х        | х     |        |

**IDC** - Design of Future ES

Multimédia

Colliding technical requirements.

# Multimedia Domain

#### HIGH PERFORMANCES

real time, portability, long battery life

#### **UP-TO-DATE SOLUTIONS**

last audio/video codecs, file formats...

#### **MORE INTEGRATED FEATURES**

MP3, Camera, Video, GPS...

#### MARKET DEMAND

convenient form factor, affordable price, fashion

# Target & Technological Challenges

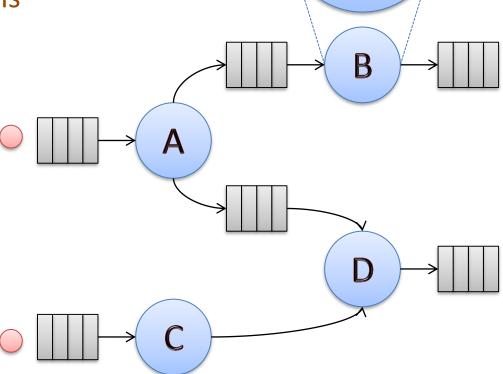

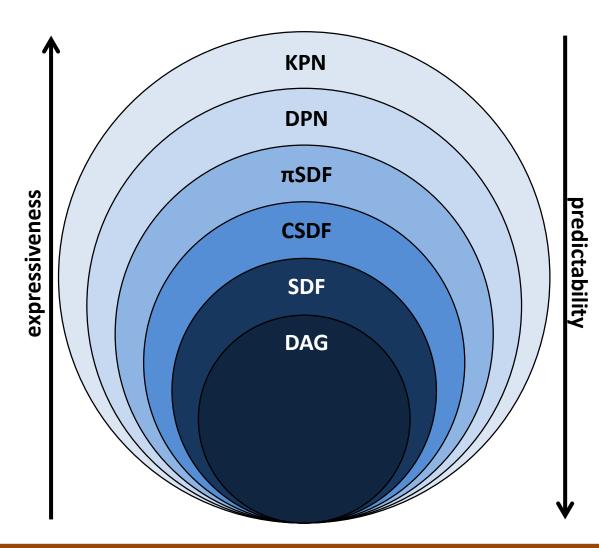

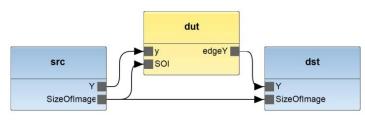

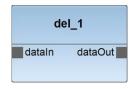

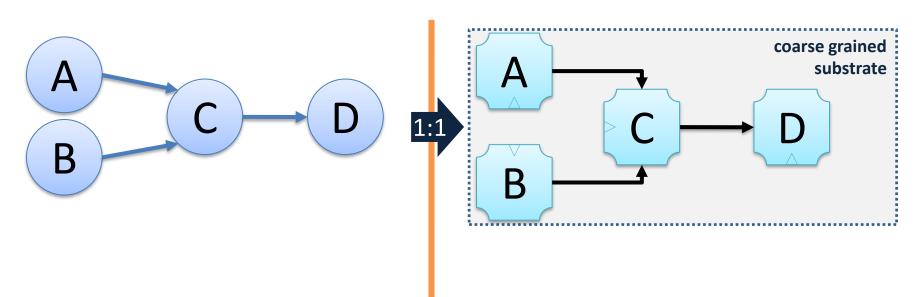

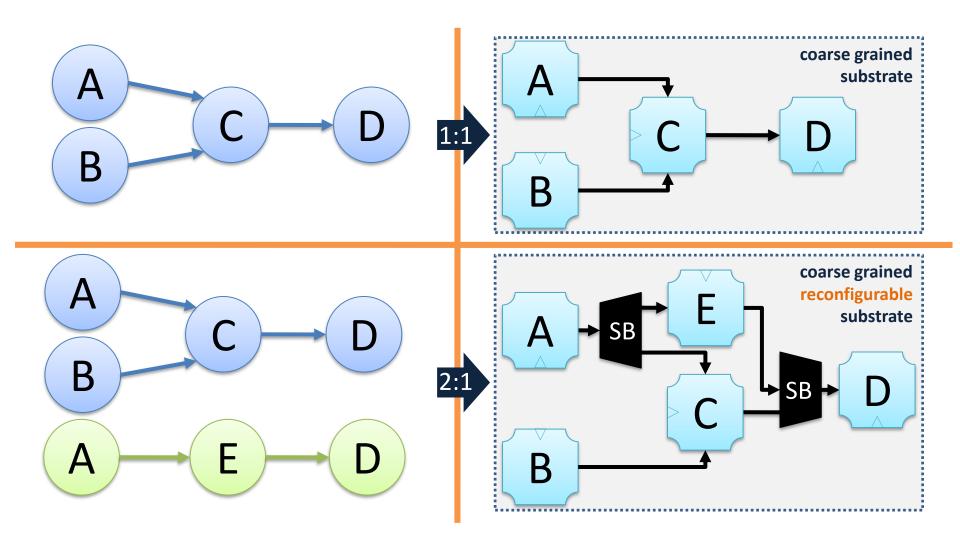

- DATAFLOW MODEL OF COMPUTATION

- Modularity and parallelism  $\rightarrow$  **EASIER INTEGRATION AND** FAVOURED RE-USABILITY

- COARSE-GRAINED RECONFIGURABILITY

- Flexibility and resource sharing → MULTI-APPLICATION PORTABLE DEVICES

(2012-2015)project has been funded bν Sardinian Regional Government (L.R. 7/2007, CRP-18324). http://sites.unica.it/rpct/

# Target & Technological Challenges

- DATAFLOW MODEL OF COMPUTATION

- Modularity and parallelism → EASIER INTEGRATION AND FAVOURED RE-USABILITY

- COARSE-GRAINED RECONFIGURABILITY

- Flexibility and resource sharing → MULTI-APPLICATION

PORTABLE DEVICES

#### **Reconfigurable Platform Composer Tool Project**

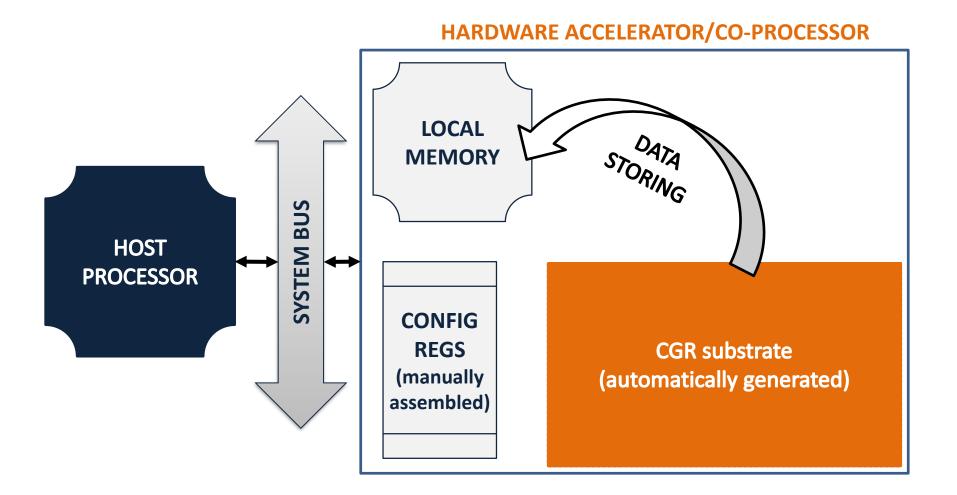

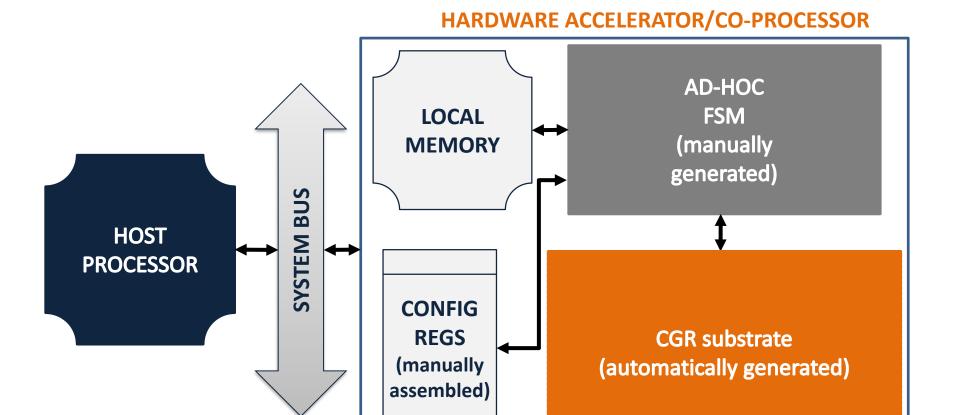

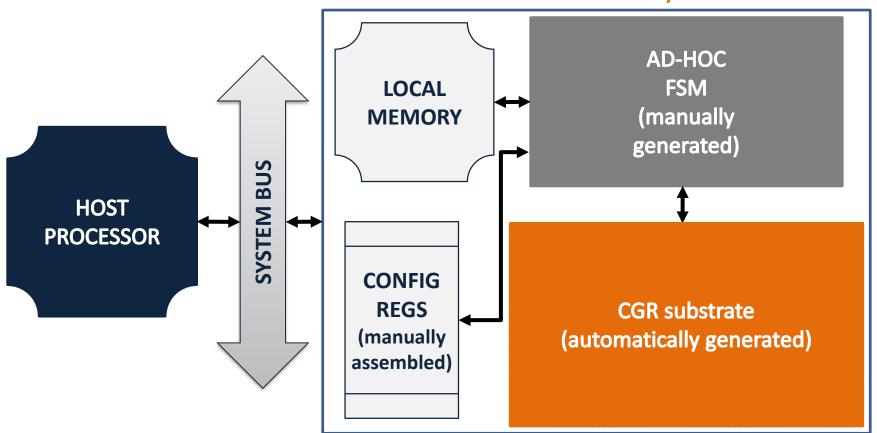

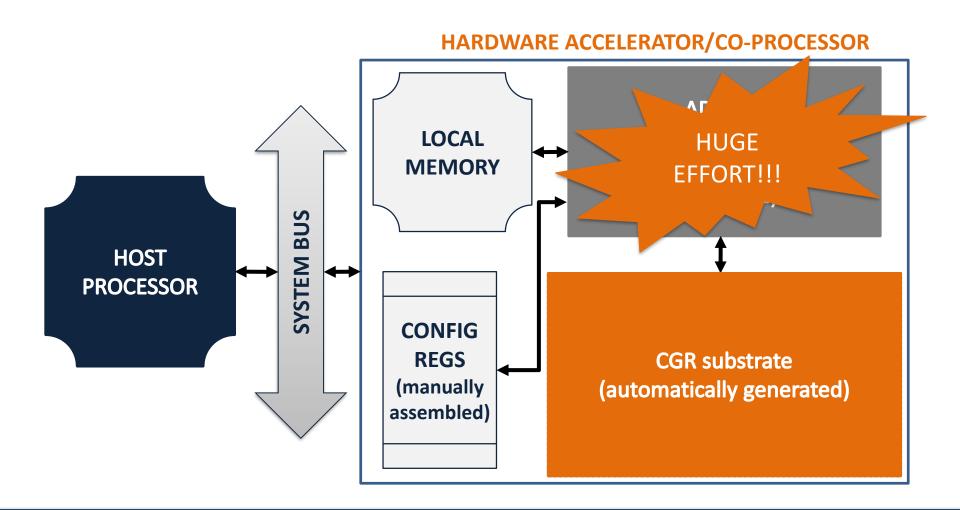

Automated **DESIGN FLOW** are fundamental to guarantee **SHORTER TIME-TO-MARKET**. Dealing with **APPLICATION SPECIFIC MULTI-CONTEXT** systems, in particular for **KERNEL ACCELERATORS**, state of the art still lacks in providing a broadly accepted solution.

The RPCT project (2012-2015) has been funded by Sardinian Regional Government (L.R. 7/2007, CRP-18324).

http://sites.unica.it/rpct/

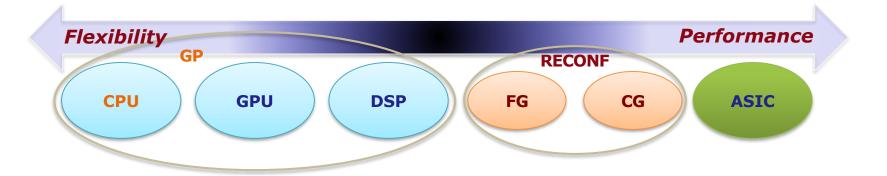

# Reasons for Coarser-Grain

# **Reasons for Coarser-Grain**

| Fine Grained | <b>Coarse Grained</b> |  |  |

|--------------|-----------------------|--|--|

| bit-level    | word-level            |  |  |

| <b>©</b>     | <b>©</b>              |  |  |

| <b>@</b>     | <b>©</b>              |  |  |

| 8            | <b>©</b>              |  |  |

|              | bit-level  ©          |  |  |

#### Coarse Grained (CG):

- both in ASIC and FPGA

- 1 clock cycle switching, with dedicated switching blocks.

#### Fine Grained (FG):

- FPGA only

- switching requires a new bitstream

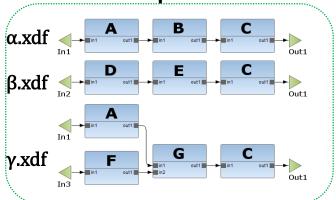

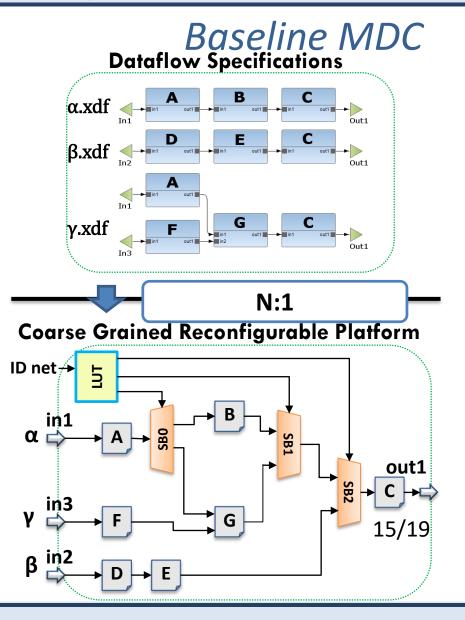

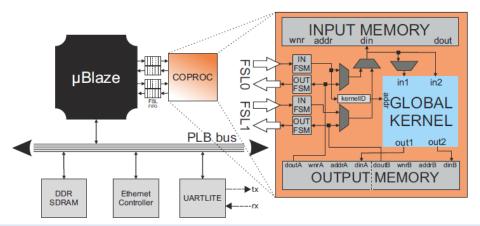

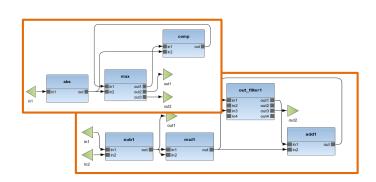

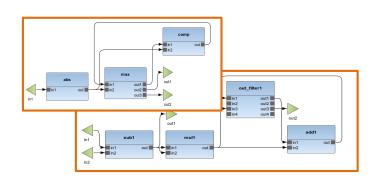

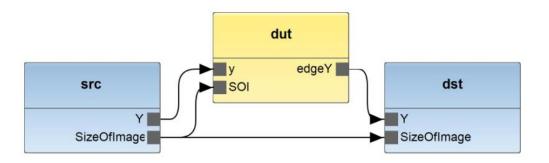

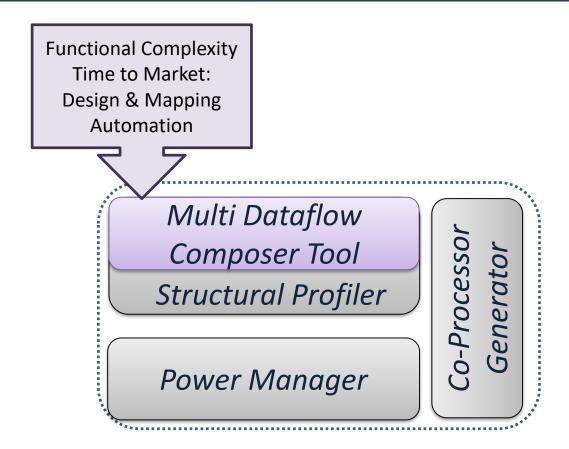

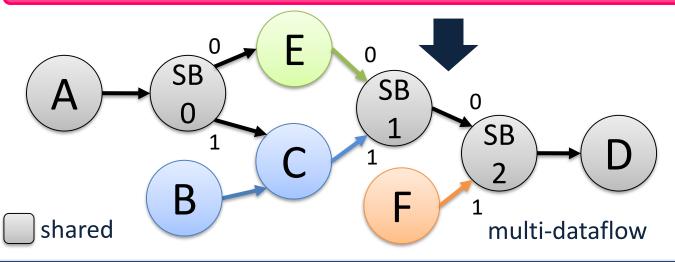

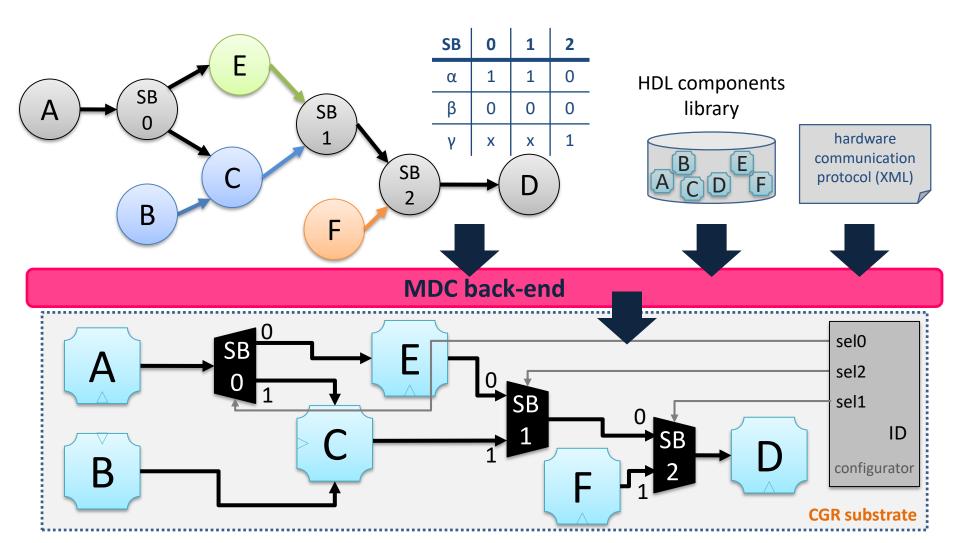

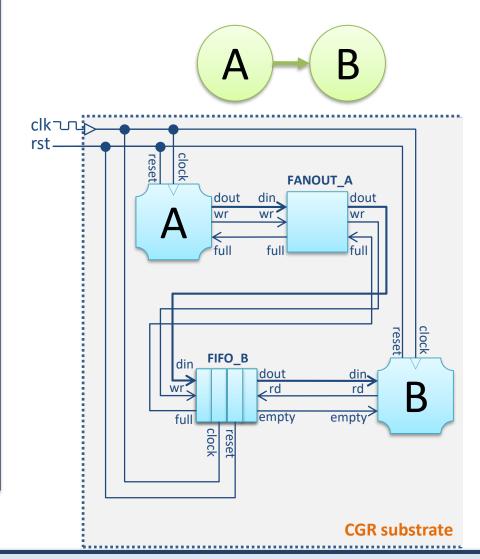

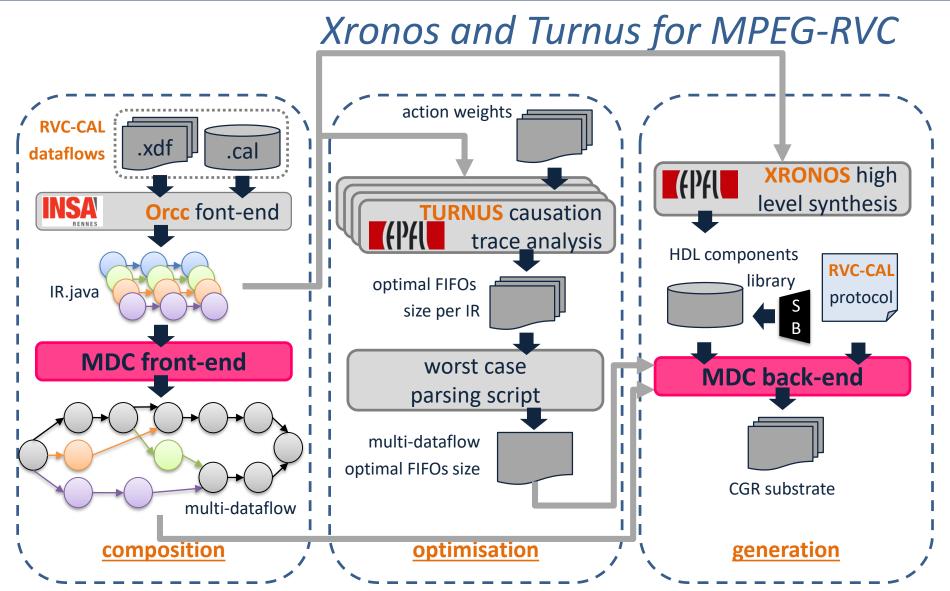

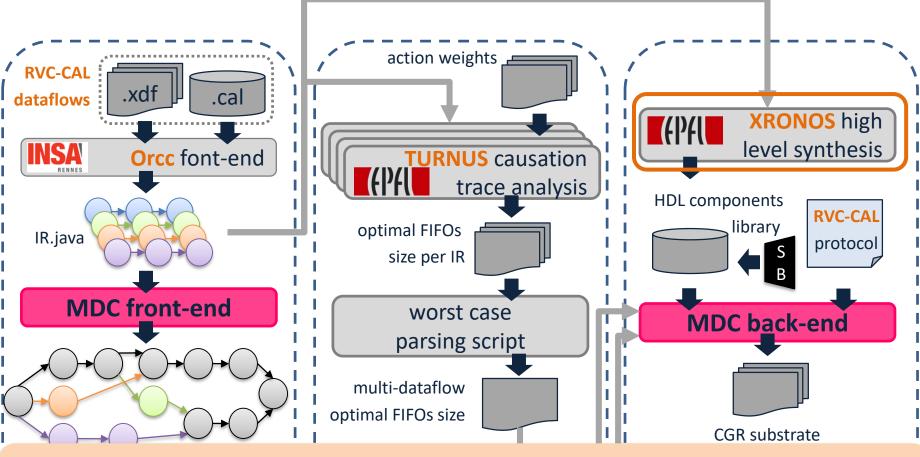

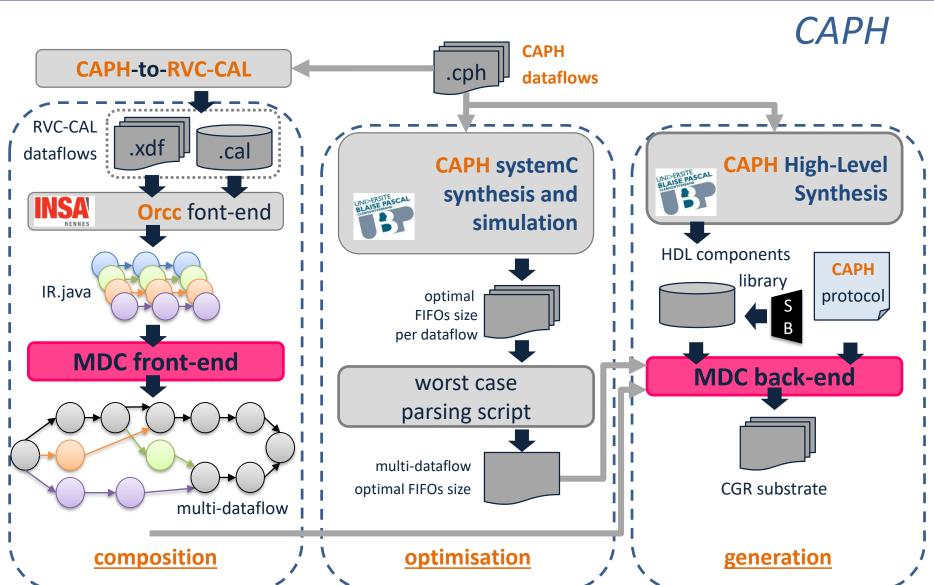

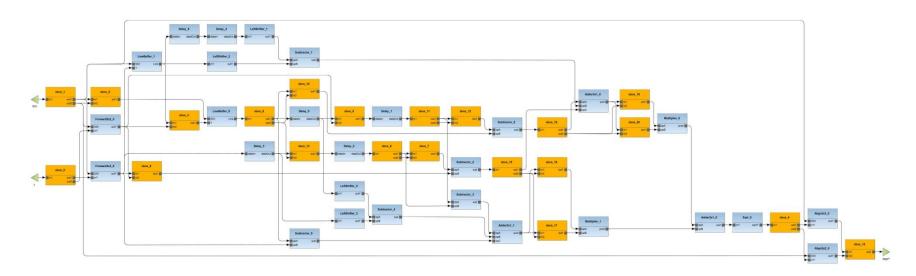

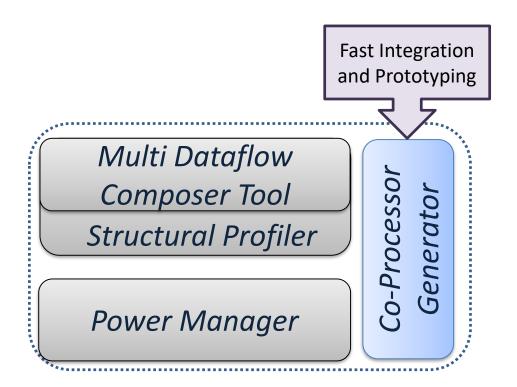

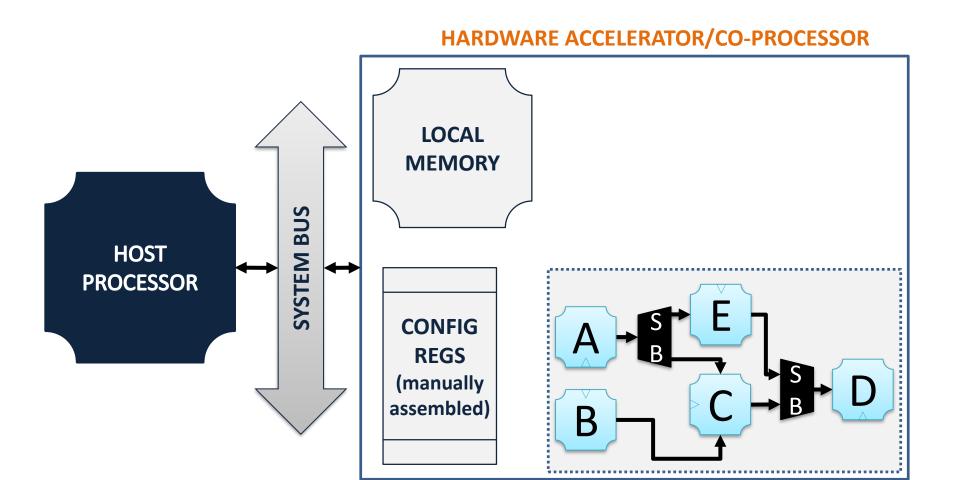

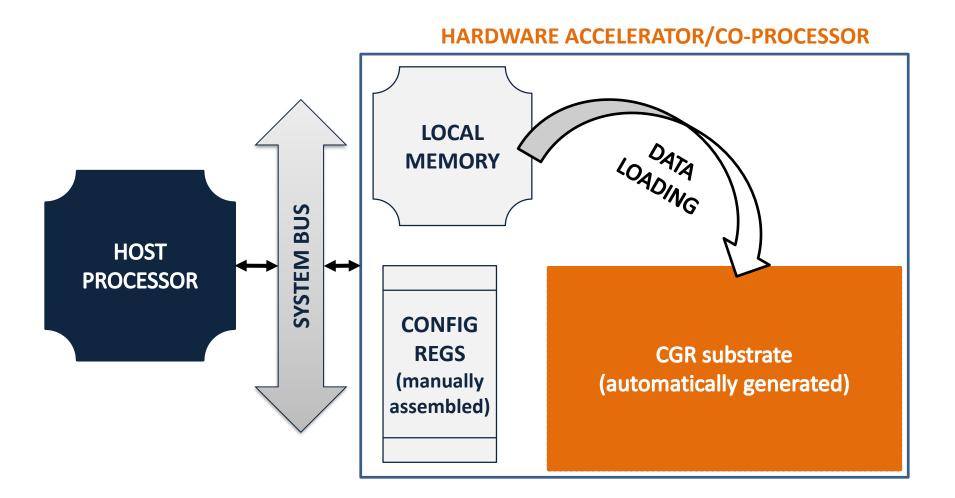

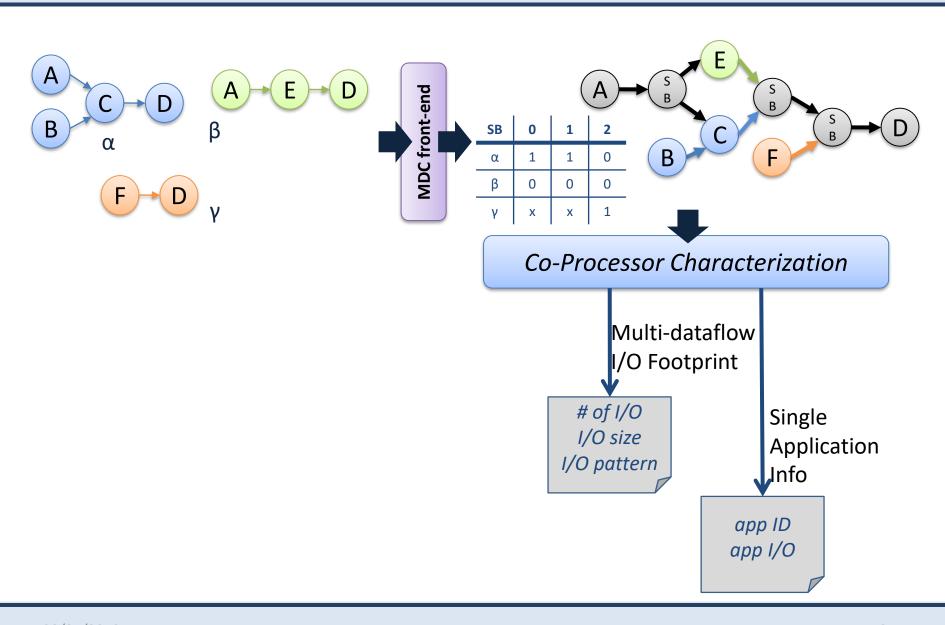

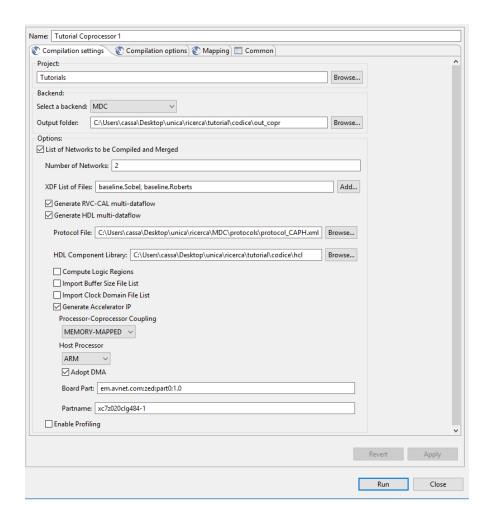

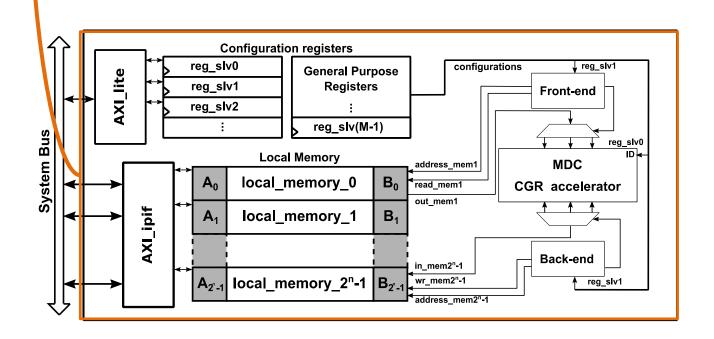

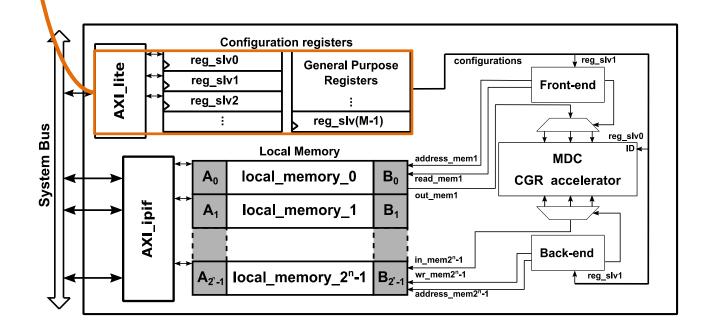

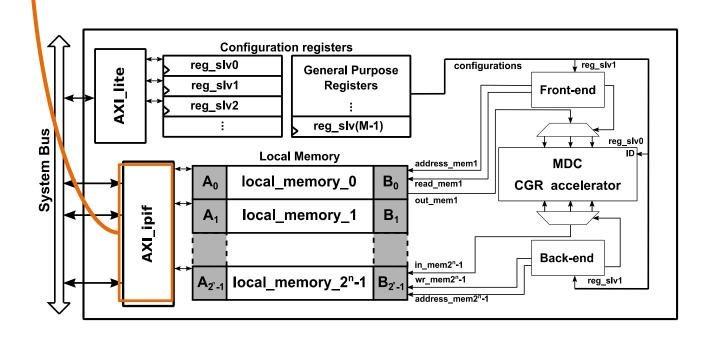

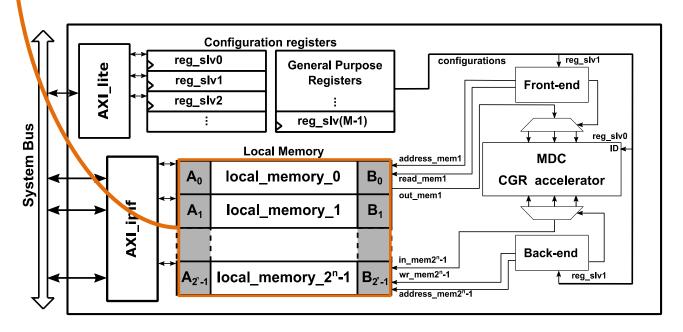

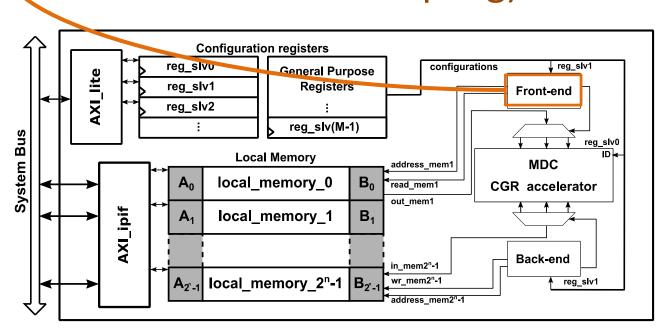

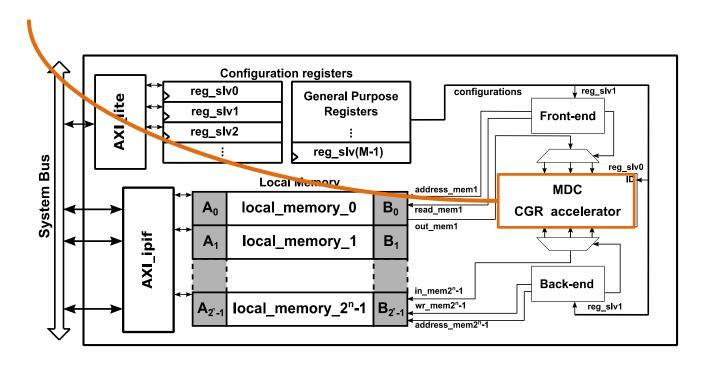

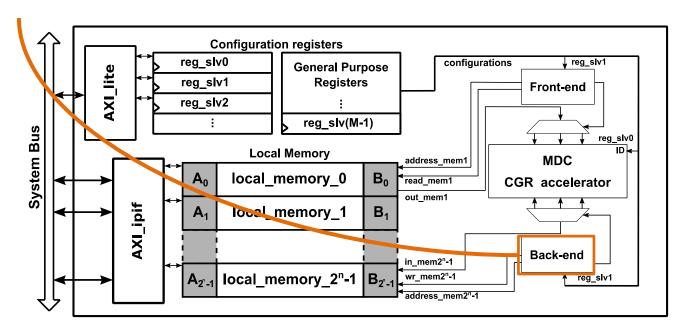

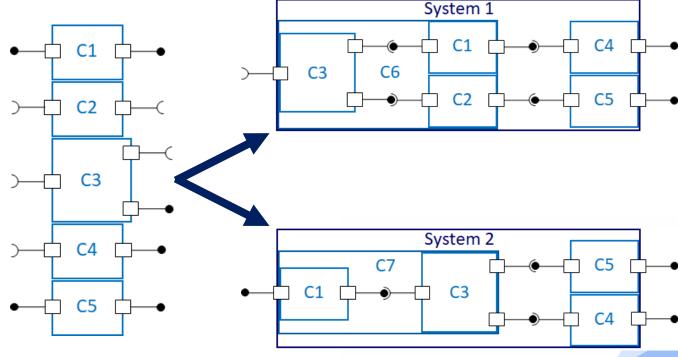

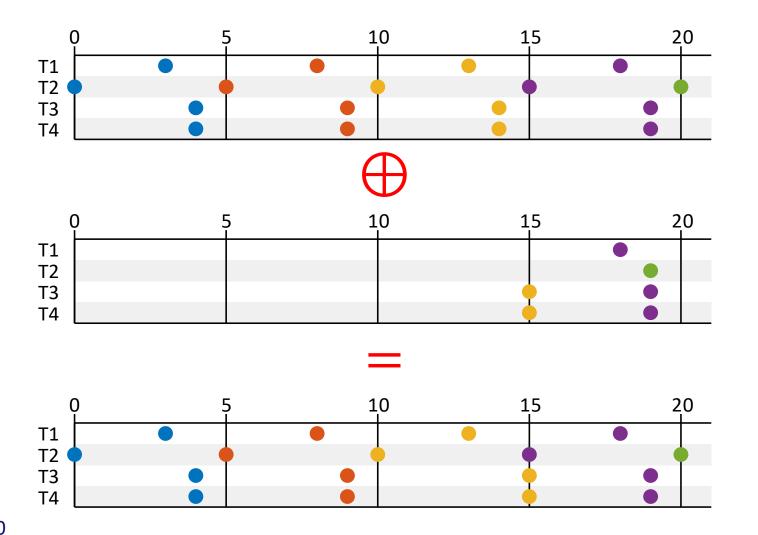

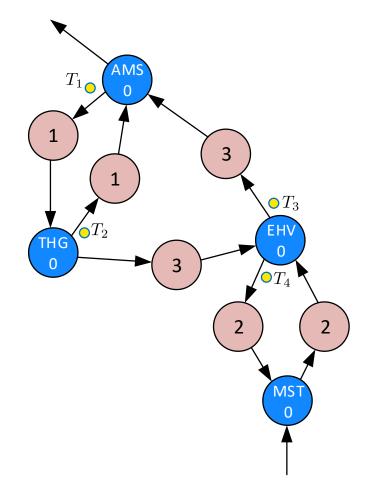

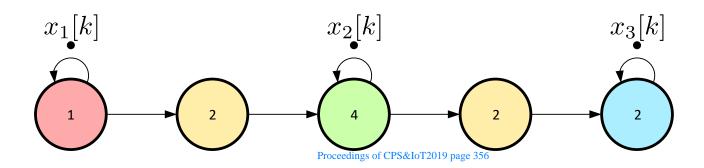

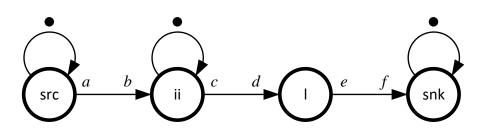

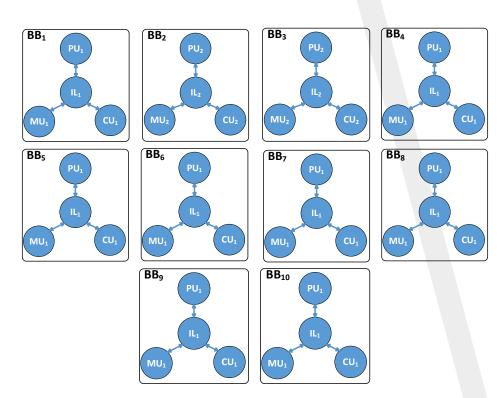

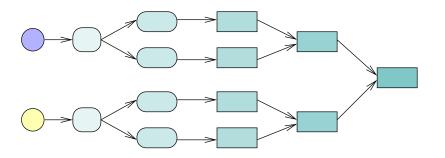

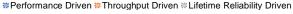

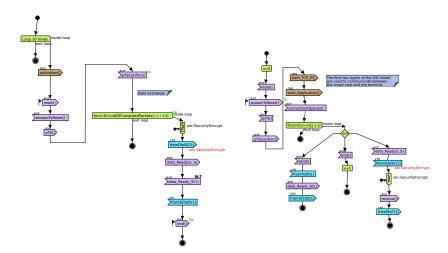

#### Baseline MDC

Multi Dataflow Composer Tool Structural Profiler

Power Manager

Co-Processor Generator

MDC design suite

http://sites.unica.it/rpct/

13/19

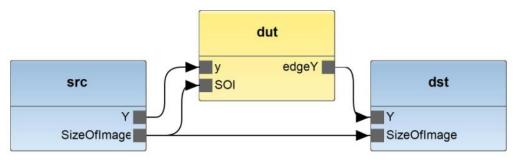

Co-Processor Generator

Multi Dataflow

Composer Tool

Structural Profiler

Power Manager

MDC design suite

http://sites.unica.it/rpct/

Baseline MDC

Dataflow Specifications

14/19

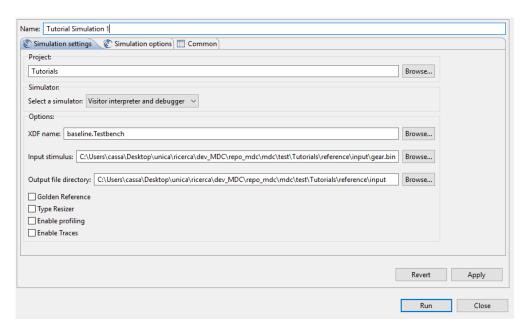

Multi Dataflow

Composer Tool

Structural Profiler

Power Manager

MDC design suite http://sites.unica.it/rpct/

Co-Processor Generator

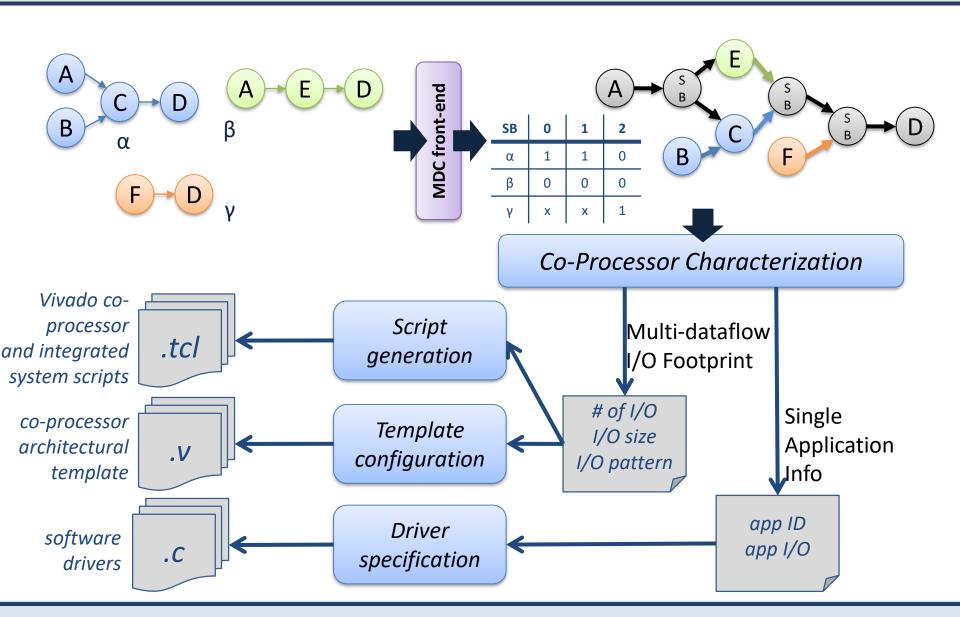

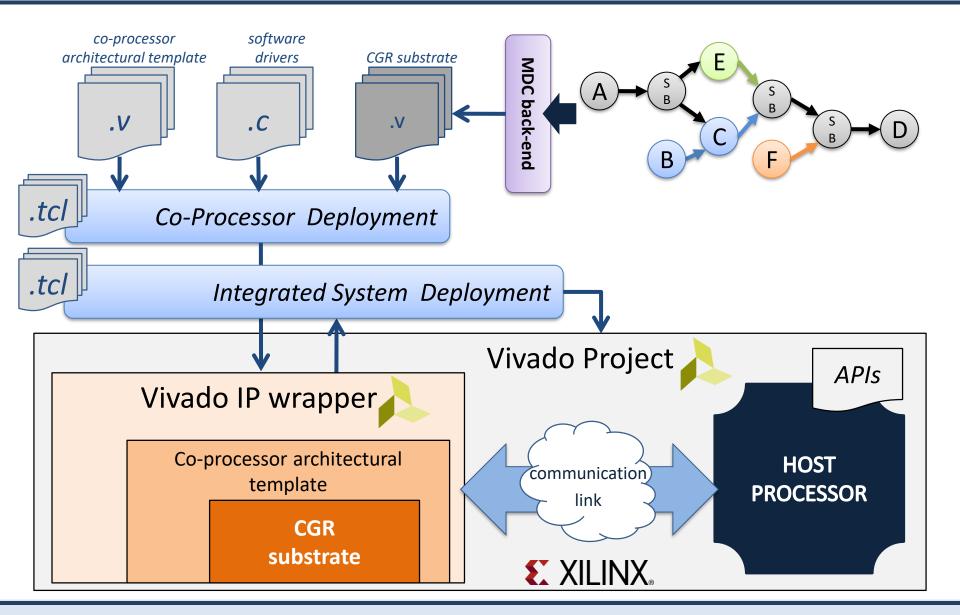

#### **Additional Features**

Multi Dataflow Composer Tool Structural Profiler

Power Manager

MDC design suite http://sites.unica.it/rpct/ Co-Processo Senerator

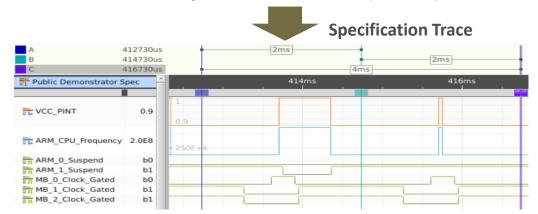

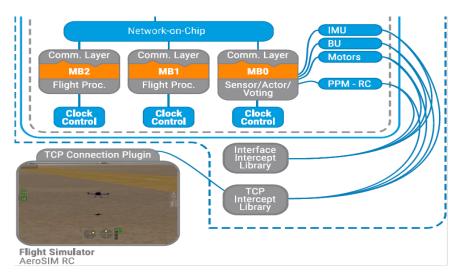

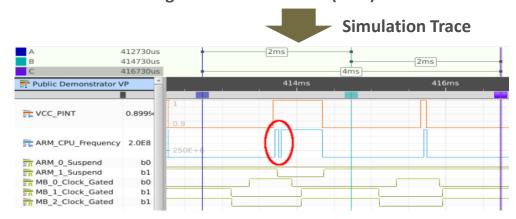

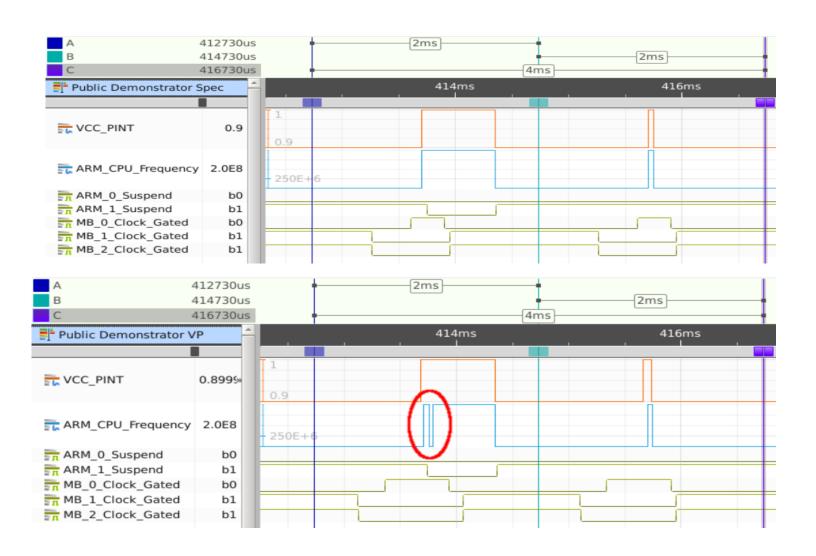

#### **Structural Profiler:**

low-level feedback (from synthesis) and DSE for topology optimization.

•(ASIC + FPGA)

#### **Co-Processor Generator:**

generation of ready-to-use Xilinx Ips

•(FPGA)

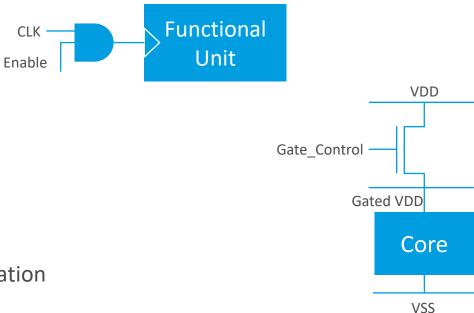

#### **Power Manager:**

automatic application of clock-gating and/or power-gating.

•CG (ASIC + FPGA)

PG(ASIC)

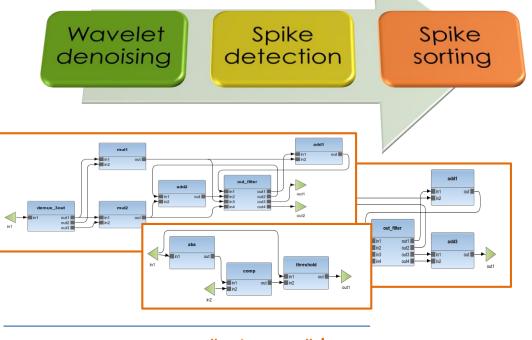

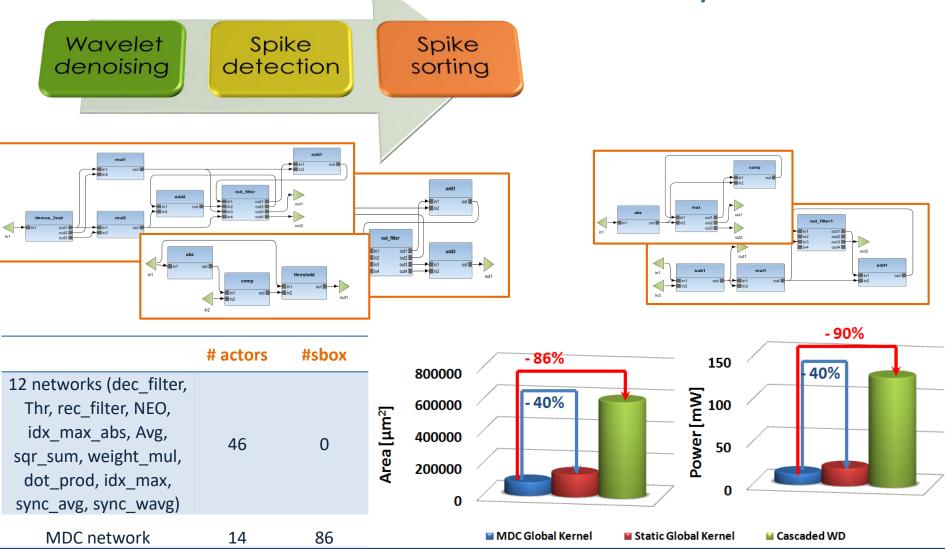

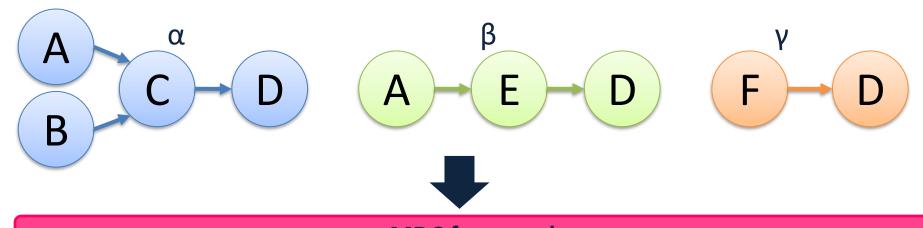

#### **MDC** suite

Context of Application

What kinds of applications can be combined with MDC?

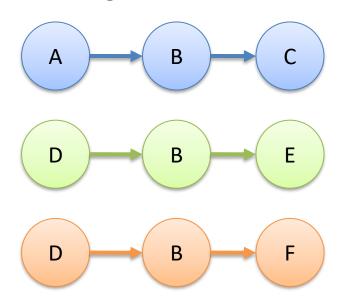

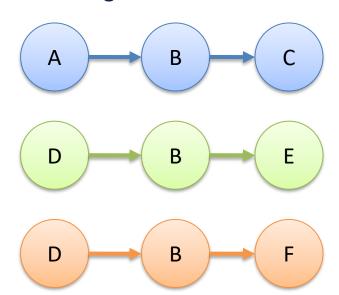

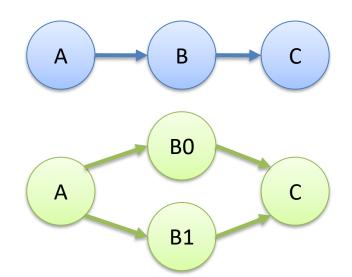

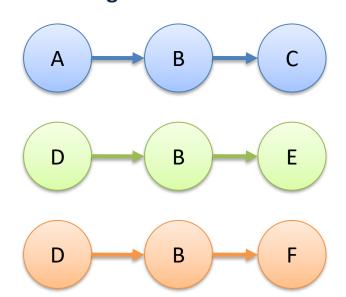

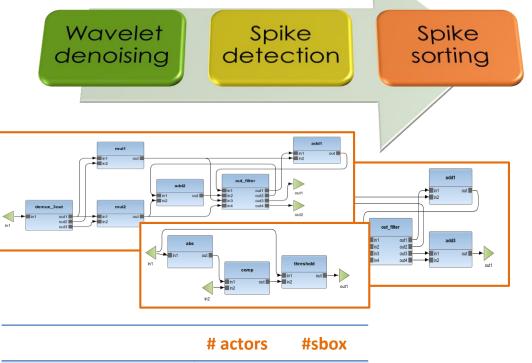

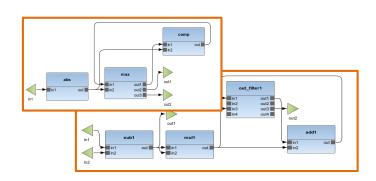

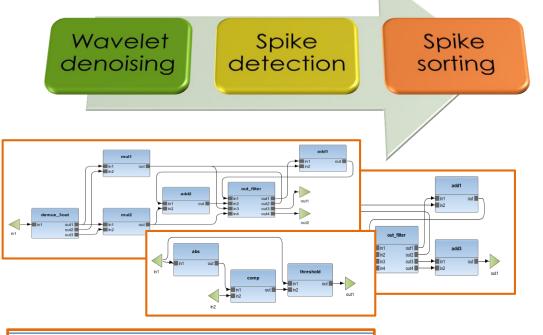

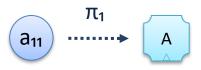

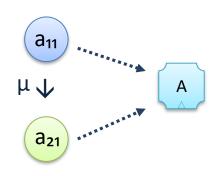

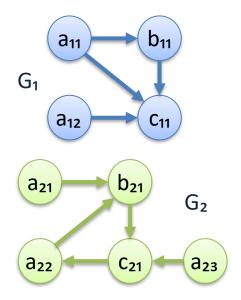

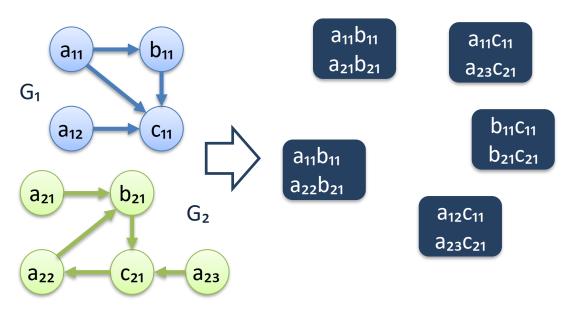

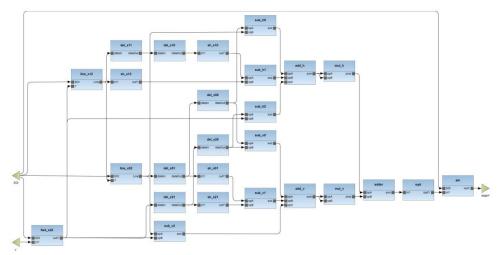

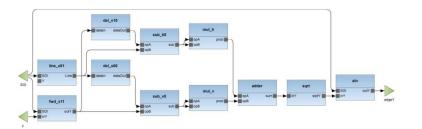

#### What kinds of applications can be combined with MDC?

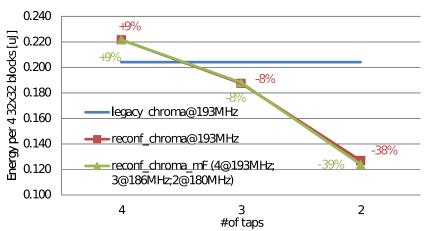

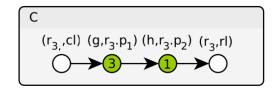

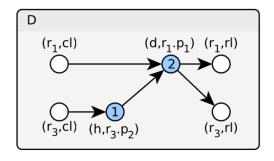

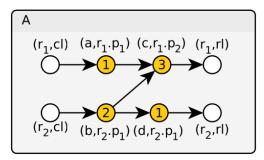

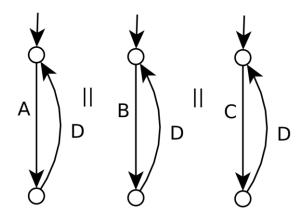

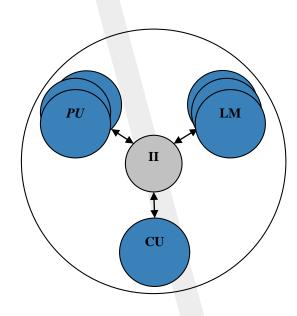

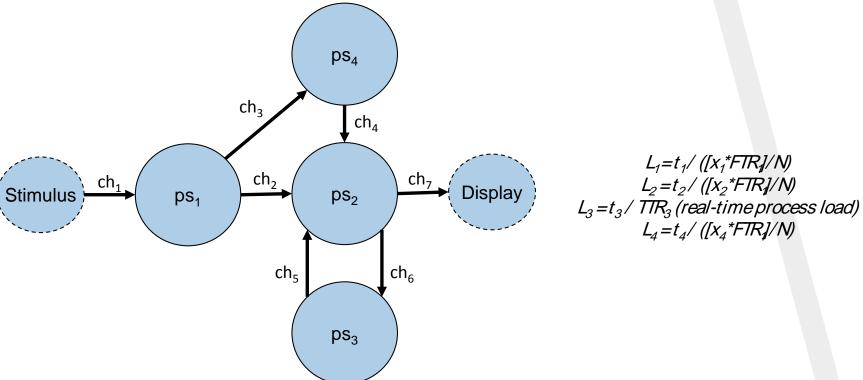

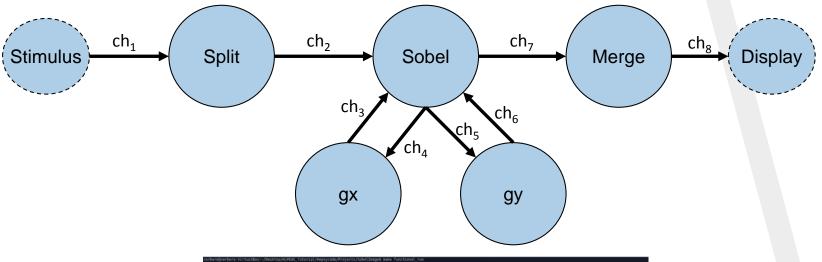

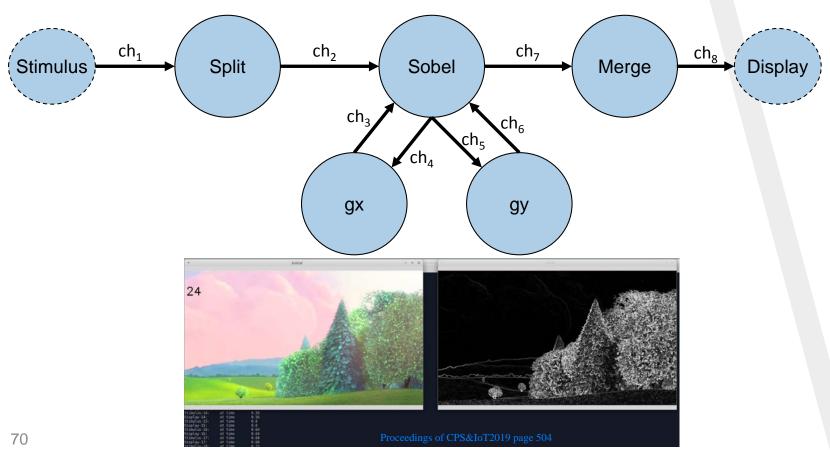

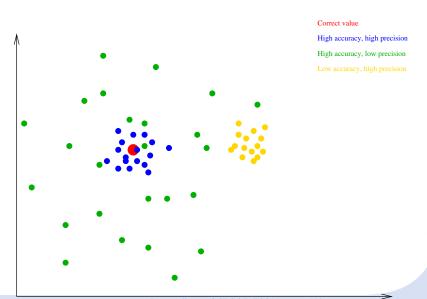

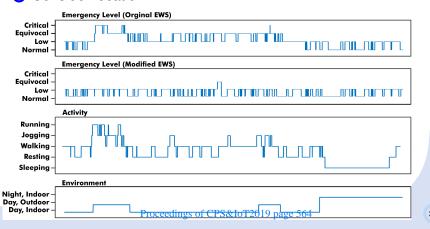

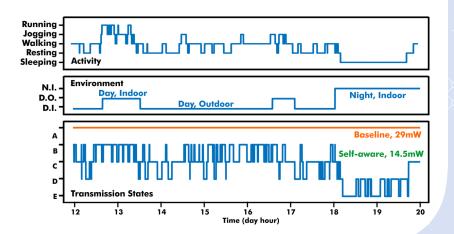

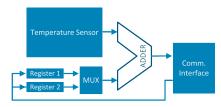

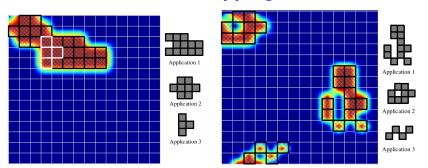

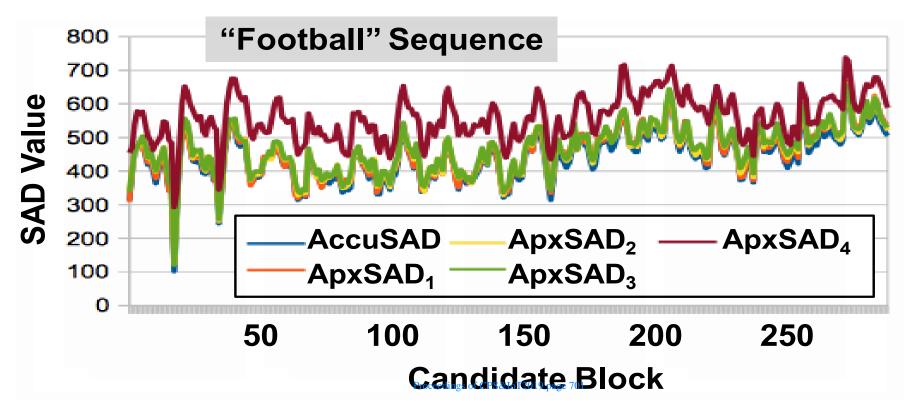

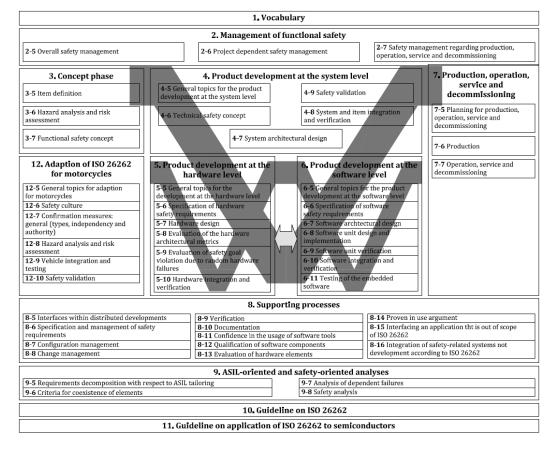

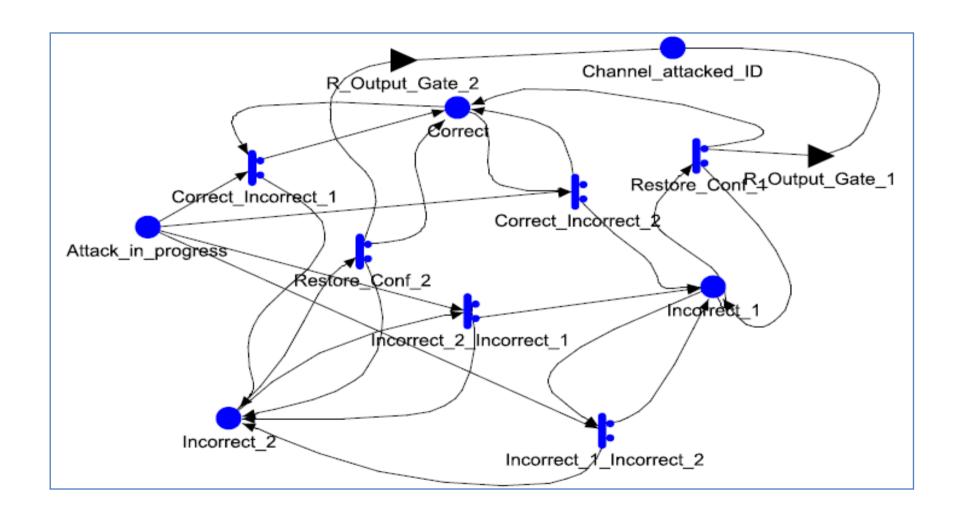

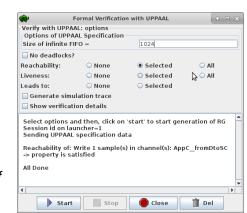

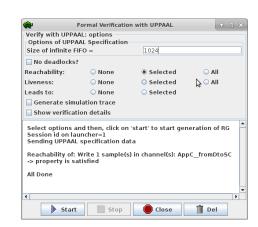

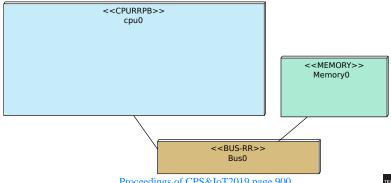

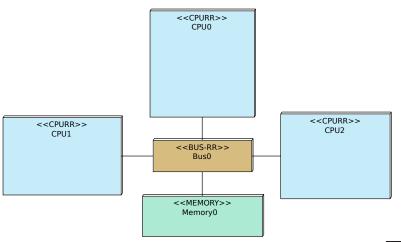

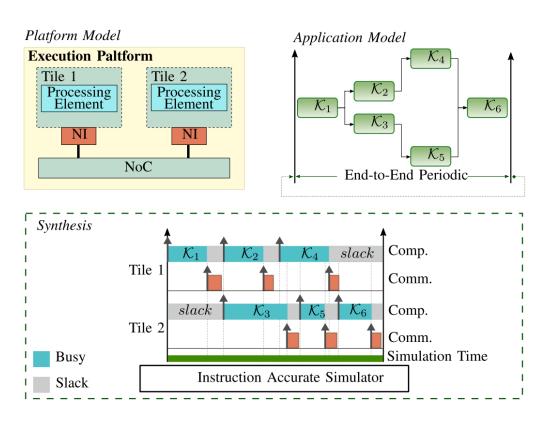

1. Different applications with common computational **operations**: it achieved by considering applications from the same application field or small actor granularities.